Test: Adders - 1 - Electrical Engineering (EE) MCQ

10 Questions MCQ Test - Test: Adders - 1

Which of the following statements about the arithmetic circuit is INCORRECT?

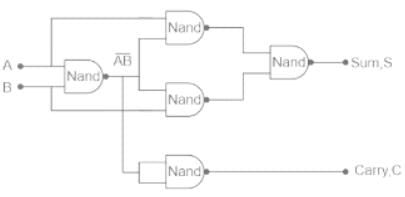

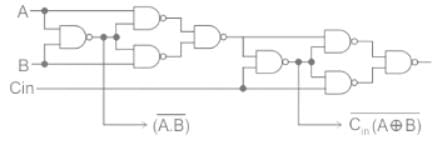

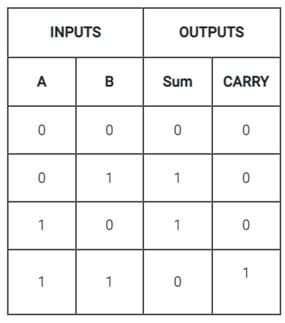

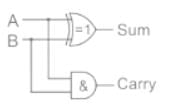

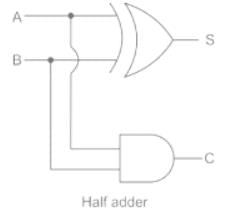

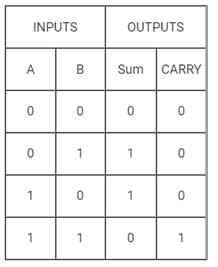

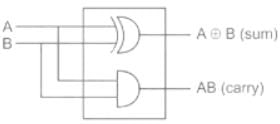

How many number of 2-input NAND gates are required to realise a half adder circuit?

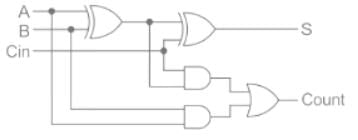

The minimum number of NAND gates requires to implement A ⊕ B ⊕ C is

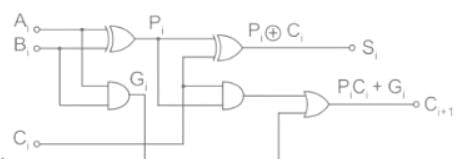

In case of the parallel adder, the speed with which an addition can be performed is governed by the time required for the carries to propagate or ripple through all the stages of the adder. Which of the following statements are correct?

(A) The method of speeding up the addition process is based on additional functions of full adder called carry generate and carry propagation.

(B) The look-ahead carry adder speeds up the process by eliminating ripple carry dely.

(C) The final sum output of the nth stage is given by Sn = Pn ⊕ Cn where Pn = An ⊕ Bn

(D) The final carry output of nth stage is given by Cn+1 = Gn + Pn where Gn = An ⋅ Bn

Choose the correct answer from the options given below:

(1) (A) and (B) only

(2) (A) and (C) only

(3) (A), (B) and (C) only

(4) (B), (C) and (D) only

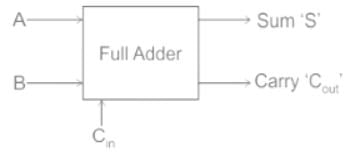

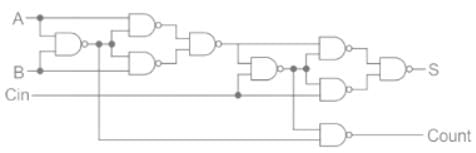

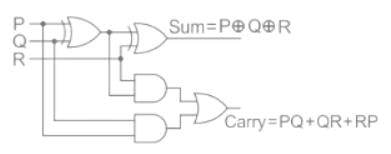

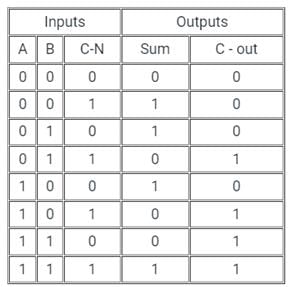

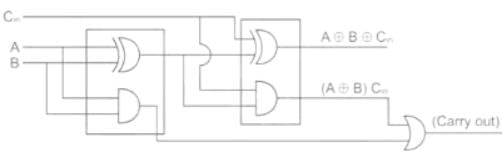

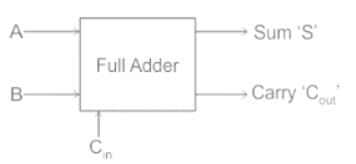

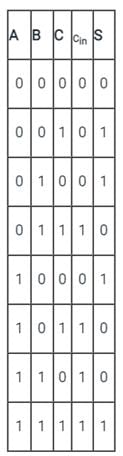

If the inputs are P, Q and R, then in the full adder, find the output expression of the sum.

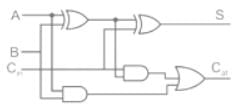

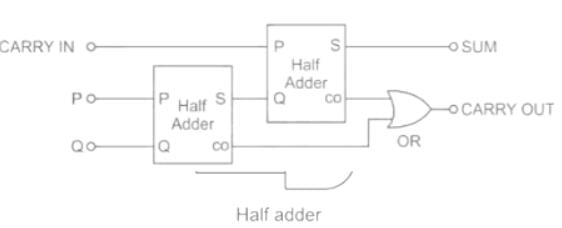

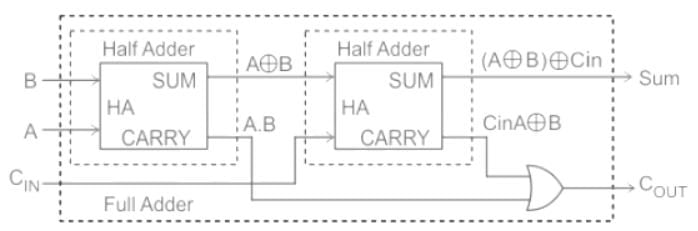

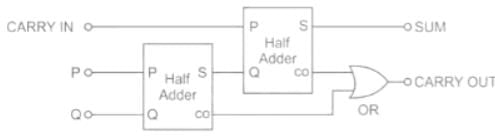

Given two half adders, what extra 2-input gate is required to build a full adder?