Binary Adders - Free MCQ Practice Test with solutions, GATE ECE Engineering

MCQ Practice Test & Solutions: Test: Binary Adders (10 Questions)

You can prepare effectively for Electronics and Communication Engineering (ECE) Digital Circuits with this dedicated MCQ Practice Test (available with solutions) on the important topic of "Test: Binary Adders". These 10 questions have been designed by the experts with the latest curriculum of Electronics and Communication Engineering (ECE) 2026, to help you master the concept.

Test Highlights:

- - Format: Multiple Choice Questions (MCQ)

- - Duration: 30 minutes

- - Number of Questions: 10

Sign up on EduRev for free to attempt this test and track your preparation progress.

In which of the following adder circuits, the carry look ripple delay is eliminated?

Detailed Solution: Question 1

For an n-bit binary adder, what is the number of gates through which a carry has to propagate from input to output?

Detailed Solution: Question 2

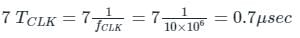

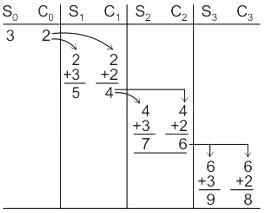

A serial adder is operating with a clock frequency of 10 MHz. Time required to sum 1010111 and 10111 number is –(in μsec)

Detailed Solution: Question 3

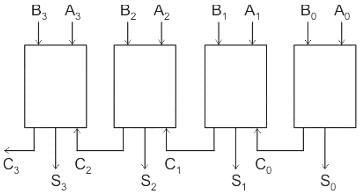

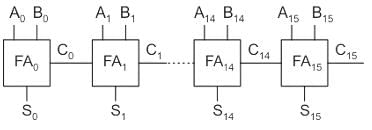

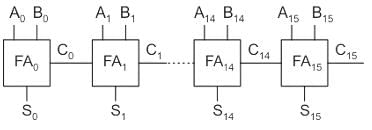

A 16-bit ripple carry adder is realized using 16 identical full adders (FA) as shown in the figure. The carry-propagation delay of each FA is 12 ns and the sum-propagation delay of each FA is 15 ns. The worst case delay (in ns) of this 16-bit adder will be __________.

Detailed Solution: Question 4

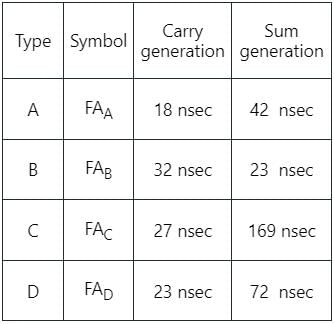

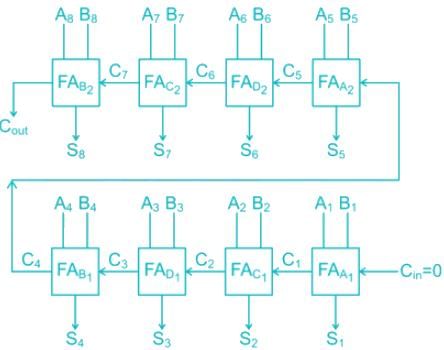

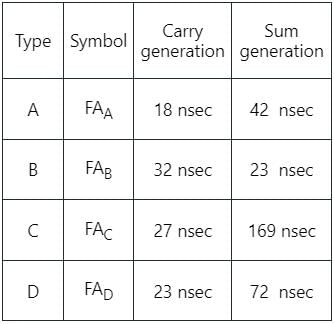

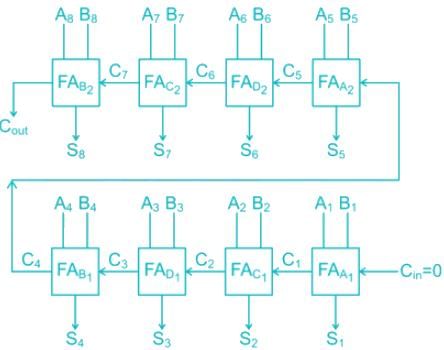

Four different types of Adders are used to construct an 8-bit adder. The characteristic of each full adder in terms of delay is as follows:

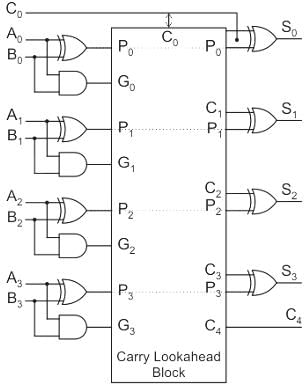

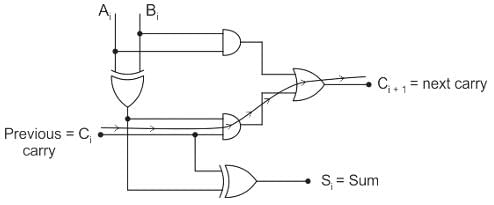

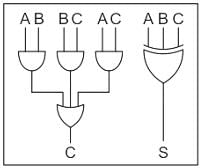

The structure of the FA is as follows:

The maximum no of addition per second that the above adder can perform is –

The structure of the FA is as follows:

The maximum no of addition per second that the above adder can perform is –

Detailed Solution: Question 5

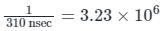

Consider a 4 bit ripple carry adder. Each full adder is implemented using a 3 input exor gate, three 2 input AND gates and one 3 input or gate. Consider the delay of 3 input exor gate to be 3 n-sec, the delay of each 2 input AND gate to be 1 nsec and the delay of each 3 input or gate to be 1 nsec. The total time taken by the 4 bit ripple carry adder to perform successful addition operation is ________.

Detailed Solution: Question 6

Let x be the number of AND gates present in the 4 bit carry look ahead adder and y be the number of OR gates presents in that adder then the value of 2x + 2y is ____________

Detailed Solution: Question 7

Detailed Solution: Question 8

The number of logic gates and the way of their interconnections can be classified as ____________

Detailed Solution: Question 9

The output sum of two decimal digits can be represented in ____________

Detailed Solution: Question 10

75 videos|190 docs|70 tests |