Test: Electronic Devices - 2 - Electronics and Communication Engineering (ECE) MCQ

20 Questions MCQ Test GATE ECE (Electronics) Mock Test Series 2025 - Test: Electronic Devices - 2

For a MOS capacitor, Vfb and Vt are the flat-band voltage and the threshold voltage, respectively. The variation of the depletion width (Wdep) for varying gate voltage (Vg) is best represented by

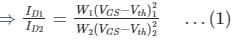

Two n-channel MOSFETs, T1 and T2, are identical in all respects except that the width of T2 is double of T1. Both the transistor are biased in the saturation region of operation, but the gate overdrive voltage (VGS - VTH) of T2 is double that of T1, where VGS and VTH are the gate-to-source voltage and threshold voltage of the transistors, respectively. If the drain current and transconductance of T1 are ID1 and gm1 respectively ; the corresponding values of these two parameters for T2 are

| 1 Crore+ students have signed up on EduRev. Have you? Download the App |

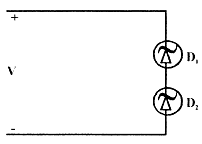

If saturation currents of 2 diodes are 1 µA and 2 µA.

If break down voltages of diode are same and are equal to 100 volt, what is value of current in D1.

Q.

If V = 90 volt

If break down voltages of diode are same and are equal to 100 volt, what is value of current in D1.

If saturation currents of 2 diodes are 1 µA and 2 µA.

If break down voltages of diode are same and are equal to 100 volt, what is value of current in D1.

Q.

If V = 110 volt

For Si transistor, if β ≥ 30 and ICBO = 10 nA The minimum value of R, for transistor to remain in active region for vi = 12 volt, is __________ kΩ.

A sample of silicon (uniformly doped n-type) at T = 300° K has the electron concentration varying linearly with distance as shown in the figure

The diffusion current is found to be −1120 A/cm2. If the diffusion constant Dn = 35 cm2/s, the electron concentration at x = 0 is

In a semiconductor sample,

where LP (hole diffusion length) = 4.8 × 10−4 cm

Hole diffusion coefficient DP = 20 cm2/s

The hole diffusion current density at x = 0 is

In the plot of log I vs V for a semiconductor Ge diode, the slope at room temperature is _________. Assume V >> VT and room temperature 27°C.

Consider a p-type semiconductor which is lightly doped i.e. condition of p >> n is not valid. p, n, ni are holes, electrons and intrinsic carrier concentration respectively. Then 2n + NA is ___________ if NA is immobile acceptor ions concentration

Consider the following network

VL is to be maintained at 10 V.

The correct representation of VL versus RL is

Consider the following sentences in respect of LEDs (Light emitting diodes) and semiconductor laser diode.

S1 : Only direct band gap type semiconductors are suitable for fabrication of LEDs.

S2 : Both direct band gap type and indirect band gap type semiconductors are suitable for fabrication of semiconductor laser diode.

Choose the best alternative

An n-channel enhancement mode MOSFET is biased at VGS > VTH and VDS > (VGS - VTH), where VGS is the gate-to-source voltage, VDS is the drain-to-source voltage and VTH is the threshold voltage. Considering channel length modulation effect to be significant, the MOSFET behaves as a

What are the states of three ideal diodes of circuit shown below:

For BJT, circuit shown assume that β of transistor is very large, if here Si transistor is used, then transistor will operate in

Consider the following circuit:

Q.

If vi is as shown

then RB and RC for the circuit concerned can be _________ and _________ respectively, if ICsat = 6 mA. Assume the transistor inverter operation

Consider the following circuit:

Q.

The V0 shall be represented by

A BJT having β = 125 is biased at a dc collector current of 1.23 mA. The values of gm, re and rπ at the bias point are: (Assume temperature of operation = 25°C).

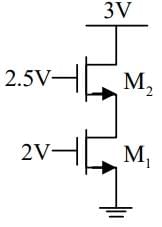

Assuming that transistor M1 and M2 are identical and have a threshold voltage of 1V, the state of transistors M1 and M2 are respectively

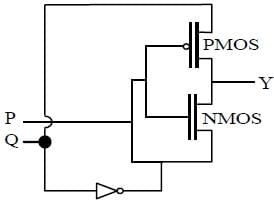

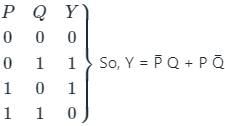

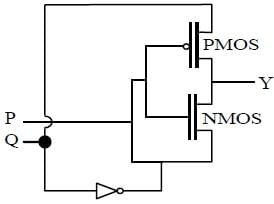

For the circuit shown in the figure, P and Q are the inputs and Y is the output.

The logic implemented by the circuit is

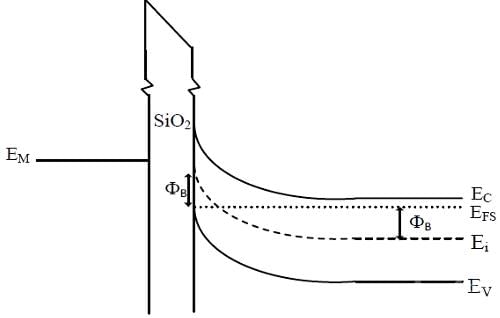

The figure shows the band diagram of a Metal Oxide Semiconductor (MOS). The surface region of this MOS is in

|

25 docs|263 tests

|

|

25 docs|263 tests

|