Microprocessor Interfacing - Free MCQ Practice Test with solutions, GATE

MCQ Practice Test & Solutions: Test: Microprocessor Interfacing (10 Questions)

You can prepare effectively for Electronics and Communication Engineering (ECE) Topicwise Question Bank for Electronics Engineering with this dedicated MCQ Practice Test (available with solutions) on the important topic of "Test: Microprocessor Interfacing". These 10 questions have been designed by the experts with the latest curriculum of Electronics and Communication Engineering (ECE) 2026, to help you master the concept.

Test Highlights:

- - Format: Multiple Choice Questions (MCQ)

- - Duration: 30 minutes

- - Number of Questions: 10

Sign up on EduRev for free to attempt this test and track your preparation progress.

The number of address lines required to address 8 K bytes of memory is

Detailed Solution: Question 1

The capacity of a memory chip is 8192 bits and it has 2048 rows. Then the organisation of the chip is

The number of memory chips of size 1 K x 4-bits required to build a memory bank of size 16 K x 8 bits is

Detailed Solution: Question 3

The maximum number of memory and I/O devices that can be addressed in a 8085 microprocessor based system is:

Detailed Solution: Question 4

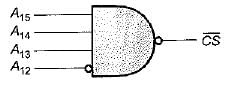

The logic circuit used to generate the active low chip select (CS) by an 8085 microprocessor to address a peripheral is shown in figure below.

The address range for which the device will respond is:

Detailed Solution: Question 5

The I/O devices in 8085 microprocessor can be used in:

Detailed Solution: Question 6

Eight memory chips of size 64 x 8 bits have their address buses connected together. What will be the size of the resultant memory?

Detailed Solution: Question 7

Consider the following statements associated with memory mapped I/O scheme of communication with microprocessor:

1. It reduces the memory space available.

2. Arithmetic or logical operation can be directly performed with I/O data.

3. The processor cannot manipulate I/O data residing in interface registers with the same instructions that are used to manipulate memory location.

4. The processor on treats an interface register as a part of the memory system.

Which of the statements given above is/are not correct?

1. It reduces the memory space available.

2. Arithmetic or logical operation can be directly performed with I/O data.

3. The processor cannot manipulate I/O data residing in interface registers with the same instructions that are used to manipulate memory location.

4. The processor on treats an interface register as a part of the memory system.

Detailed Solution: Question 8

An 8-bit microcontroller has an external RAM with the memory map from 8000 H to 9FFF H. The number of bytes this RAM can store is:

Detailed Solution: Question 9

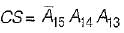

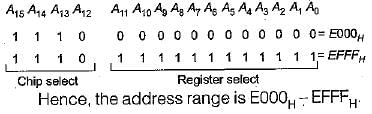

What is the address range for 4 K RAM used in 8085 microprocessor if  's used as the chip select logic?

's used as the chip select logic?

's used as the chip select logic?

's used as the chip select logic?Detailed Solution: Question 10

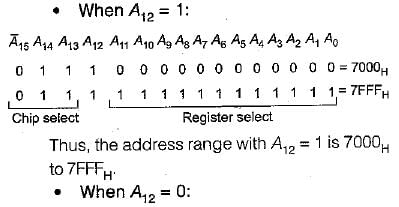

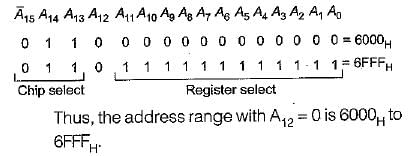

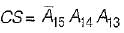

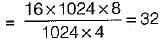

signal to be low, we have:

signal to be low, we have:

. So, the address lines A15 = 0, A14 = 1 and A13 = 1. The line A12 may be 0 or 1 and hence we will get separate range corresponding to A12 = 1 and A12 = 0

. So, the address lines A15 = 0, A14 = 1 and A13 = 1. The line A12 may be 0 or 1 and hence we will get separate range corresponding to A12 = 1 and A12 = 0