Test: Sequential Circuits- 2 - Computer Science Engineering (CSE) MCQ

15 Questions MCQ Test GATE Computer Science Engineering(CSE) 2026 Mock Test Series - Test: Sequential Circuits- 2

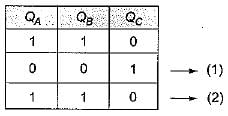

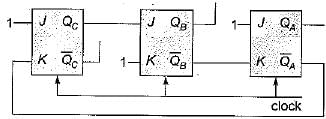

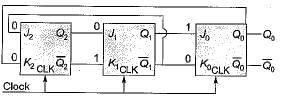

If the initial state QA QB QC = 110, after how many clocks it get back same value

If the initial state QA QB QC = 110, after how many clocks it get back same value

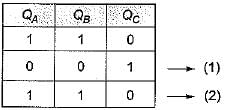

What will be the current state after two clock pulses further from the number of pulses obtained from the above question?

What will be the current state after two clock pulses further from the number of pulses obtained from the above question?

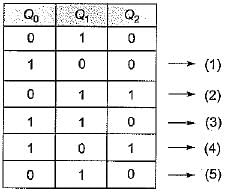

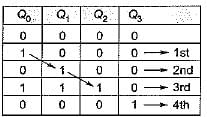

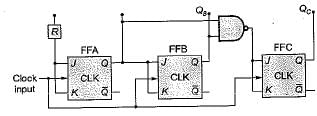

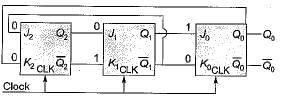

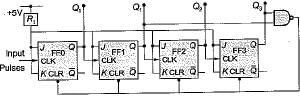

The divide by N counter as shown in figure. If initially Q0 = 0, Q1 = 1, Q2 = 0. What is the value of N?

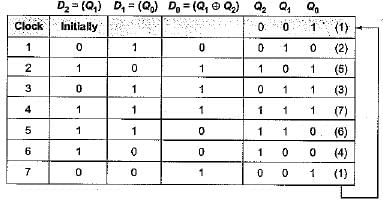

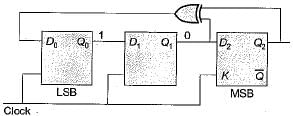

Consider the circuit given below with initial state Q0 = 1; Q1 = Q2 = 0. The state of the circuit is given by the value 4Q2 + 2Q1 + Q0

Which one of the following is the. correct state sequence of the circuit?

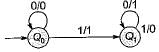

The following diagram represents a finite state machine which takes as input a binary number from the least significant bit

Which one of the following is TRUE?

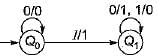

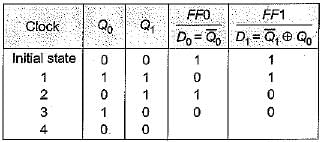

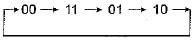

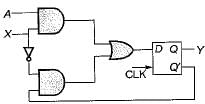

Consider the following circuit

The flip-flops are positive edge triggered DFFs. Each state is designated as a two bit string Q0Q1 Let the initial state be 00. The state transition sequence is:

The functional difference between SR flip-flop and JK flip-flop is that JK flip-flop

The number of flip-flops required in a modulo N counter is

Consider the figure given below:

Initially all flip-flops are cleared. How many dock pulse have to be applied to the system before the output from FF3 becomes a HIGH level?

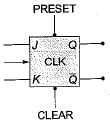

The inputs of the J-K flip-flop, shown below are:

PRESET = CLEAR = 1; J = K = 0

If a single clock pulse is applied the device will

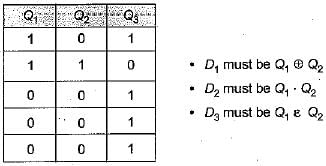

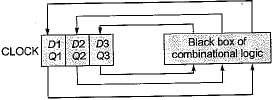

Consider the following control circuit which contains a 3-bit register and a black box with some combinational logic

The initial state of the circuit is Q1 Q2 Q3 = 000.

The circuit generates the control sequence.

(010) → ( 110) → ( 001) →(001) → . . . → ( 001)

On successive clock cycles. Which of the following sets of equations are implemented by the combinational logic in the black box?

‘n’ flip-flop will divide the clock frequency by a factor of

Let an an-1 ... a1 a0 be the binary representation of an integer b. The integer b is divisible by 3 if

If a clock with time period 'T' is used with n stage shift register, the output of final stage will be delayed by

|

57 docs|215 tests

|

|

57 docs|215 tests

|