Test: Shift Registers - 2 - Electrical Engineering (EE) MCQ

10 Questions MCQ Test Digital Electronics - Test: Shift Registers - 2

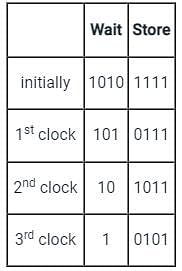

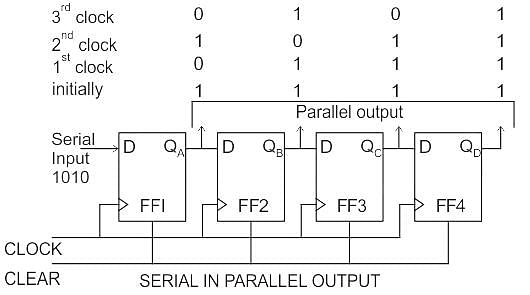

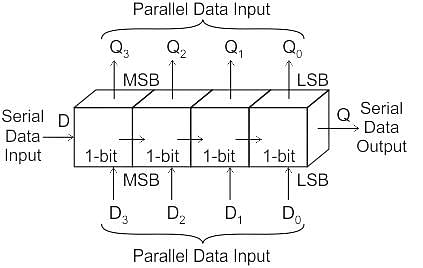

A 4 bit serial in parallel out shift register is initially set to 1111. The data 1010 is applied to the input. After 3 clock cycles the output will be:

Observe the below code and choose the correct option.

architecture behave of ckt is

signal temp: std_logic vector (7 downto 0);

begin

process(clock)

begin

if (clock’event and clock=’1’) then

for i in 0 to 6 loop

temp(i + 1) <= temp(i);

end loop;

temp(0) <= sin;

end if;

end process;

sout <= temp(7);

end behave;

| 1 Crore+ students have signed up on EduRev. Have you? Download the App |

What is the time delay (td) of an 8-bit serial in/serial out shift register with a clock frequency of 4 MHz?

To carry out multiple shift operations in a single clock cycle

Assume that a 4-bit serial in/serial out shift register is initially clear. Bits are shifted in from left. We wish to store the nibble 1100. What will be the 4-bit pattern after the second clock pulse?

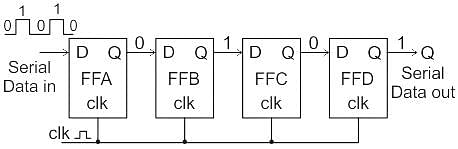

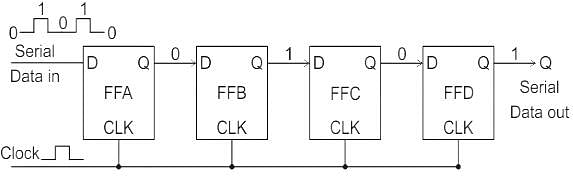

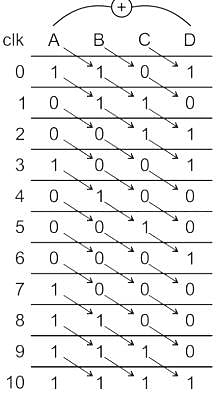

The shift register shown in the figure is initially loaded with the bit pattern 1010. Subsequently, the shift register is clocked, and with each clock pulse the pattern gets shifted by a one-bit position to the right With each shift, the bit at the serial input is pushed to the leftmost position (MSB) After how many clock pulses will the content of the shift register become 1010 again?

What is the output after two clock pulses for a bit sequence 1101 serially entered into a 4-bit parallel out shift register which is initially clear?

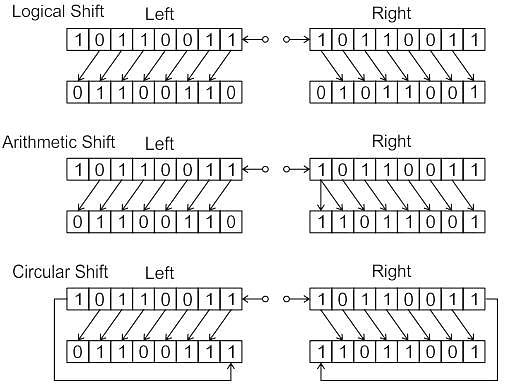

Which of the following is/are the types of shifts in shift registers?

Which of the following statements is not correct about a universal shift register?

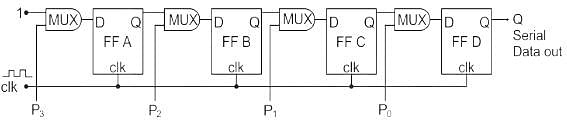

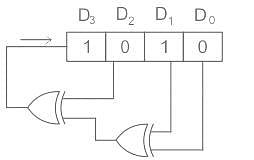

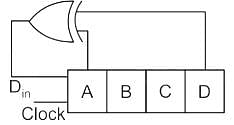

A 4-bit shift register circuit configured for right-shift operation, i.e. Din → A, A → B, B → C, C → D, is shown. If the present state of the shift register is ABCD = 1101, the number of clock cycles required to reach the state ABCD = 1111 is ________.

|

115 videos|71 docs|58 tests

|

|

115 videos|71 docs|58 tests

|