Test: Shift Registers - Electronics and Communication Engineering (ECE) MCQ

10 Questions MCQ Test Digital Circuits - Test: Shift Registers

An 8-bit serial in/serial out shift register is used with a clock frequency of 2 MHz to achieve a time delay (td) of ________

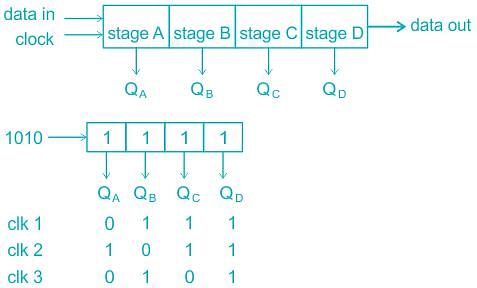

A 4-bit serial-in parallel-out shift register is initially set to 1111. The data 1010 is applied to the input. After 3 clock cycles the output will be:

| 1 Crore+ students have signed up on EduRev. Have you? Download the App |

The group of bits 11001 is serially shifted (right-most bit first) into a 5-bit parallel output shift register with an initial state 01110. After three clock pulses, the register contains ________

How can parallel data be taken out of a shift register simultaneously?

With a 200 kHz clock frequency, eight bits can be serially entered into a shift register in ________

Assume that a 4-bit serial in/serial out shift register is initially clear. We wish to store the nibble 1100. What will be the 4-bit pattern after the second clock pulse? (Right-most bit first)

A shift register that will accept a parallel input or a bidirectional serial load and internal shift features is called as?

Based on how binary information is entered or shifted out, shift registers are classified into _______ categories.

|

6 videos|76 docs|52 tests

|

|

6 videos|76 docs|52 tests

|