Test: Data Path & Control Unit - Computer Science Engineering (CSE) MCQ

10 Questions MCQ Test - Test: Data Path & Control Unit

Which of the following control signals has separate destinations?

How many address lines and data lines are required to provide a memory capacity of 16K x 16?

What is/are the advantages of using microprogramming as compared to hardwired method in implementation of control unit?

Which of the following is considered to be the brain of a computer system?

EBCDIC coding scheme uses ______ bits to code different characters.

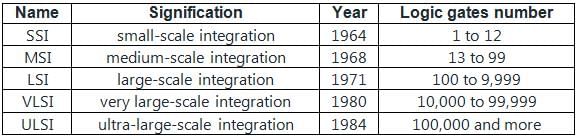

A chip having 150 gates will be classified as ________.

Given below are two statements:

Statement I: Hardwired control unit can be optimized to produce fast mode of operation.

Statement II: Indirect addressing mode needs two memory reference to fetch the operand.

In the light of the above statements. choose the correct answer from the options given below

Which of the following affects the processing power assuming they do not influence each other.

- Data bus capability

- Addressing scheme

- Clock speed

Which component of the computer is used to resolve the difference between CPU and the peripheral device?

Dynamic RAM (DRAM) is slower than Static RAM (SRAM) because _________