Logic Gates - Free MCQ Practice Test with solutions, Regulatory Body Exams

MCQ Practice Test & Solutions: Test: Logic Gates (10 Questions)

You can prepare effectively for Regulatory Body Exams Computer Awareness for Competitive Exams with this dedicated MCQ Practice Test (available with solutions) on the important topic of "Test: Logic Gates". These 10 questions have been designed by the experts with the latest curriculum of Regulatory Body Exams 2026, to help you master the concept.

Test Highlights:

- - Format: Multiple Choice Questions (MCQ)

- - Duration: 30 minutes

- - Number of Questions: 10

Sign up on EduRev for free to attempt this test and track your preparation progress.

Detailed Solution: Question 1

Examine these two statements carefully and select the answers to these items using the code given below:

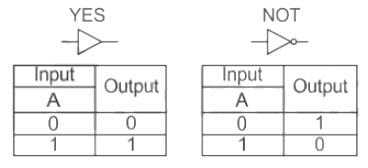

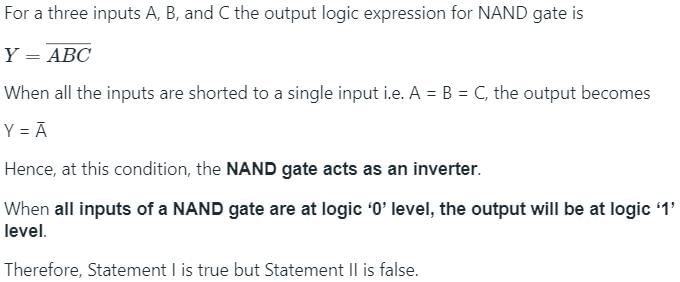

Statement (I): When all inputs of a NAND gate are shorted to get a single input, single output gate, it becomes an inverter.

Statement (II): When all inputs of a NAND gate are at logic ‘0’ level, the output is at logic ‘0’ level.

Detailed Solution: Question 2

Detailed Solution: Question 3

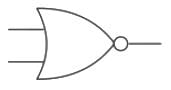

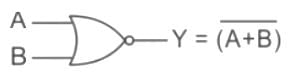

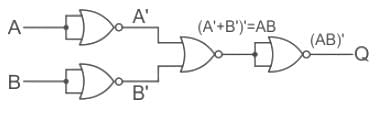

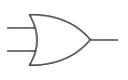

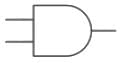

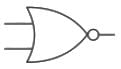

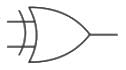

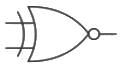

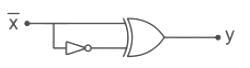

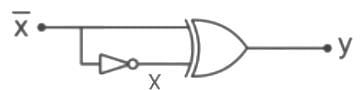

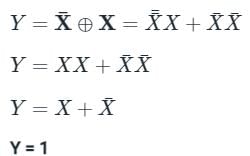

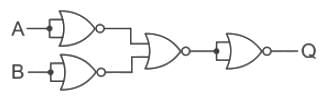

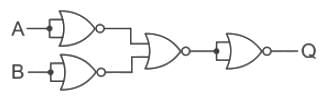

The output of logic circuit given below represents _______ gate.

Detailed Solution: Question 4

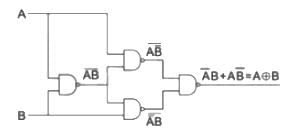

The minimum number of 2-input NAND gates required to implement a 2-input XOR gate is

Detailed Solution: Question 5

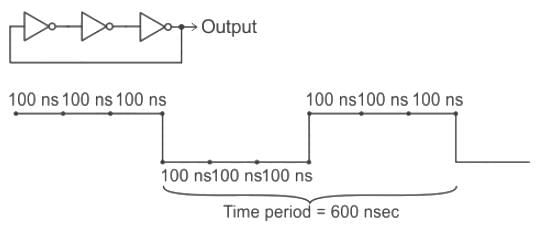

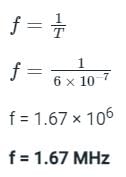

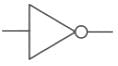

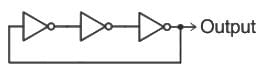

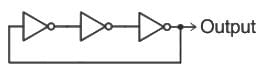

What will be the fundamental frequency for the following circuit if each inverter delay is 100 nsec?

Detailed Solution: Question 6

How many AND and OR gates are required to realise Y = AB + BC + CD?

Detailed Solution: Question 7

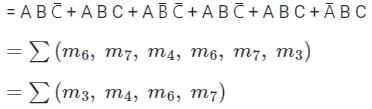

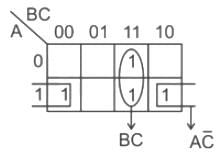

Detailed Solution: Question 8

Detailed Solution: Question 9

Detailed Solution: Question 10

30 videos|72 docs|62 tests |