Test: Sequential Circuits - Electronics and Communication Engineering (ECE) MCQ

10 Questions MCQ Test Digital Circuits - Test: Sequential Circuits

The expression for MOD number for a ripple counter with N flip-flops is

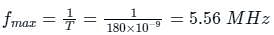

Calculate the maximum clock frequency at which a 4-bit asynchronous counter can work reliably. Assume the propagation delay of each flip-flop to be 40 ns and the width of the strobe pulse to be 20 ns.

| 1 Crore+ students have signed up on EduRev. Have you? Download the App |

A cascade of three identical modulo-5 counters has an overall modulus of

A 6 bit counter is used to count from 0, 1, 2, ......n. The value of n is _____

An eight-bit binary ripple UP counter with a modulus of 256 is holding the count 01111111. What will be the count after 135 clock pulses?

In a D flip flop, if the present state is 1, what will be the next state of the output at the complement end?

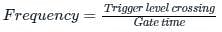

A frequency counter needs to measure a frequency of 30 Hz. If the gating time is 2 seconds then determine how many times the trigger level has been crossed?

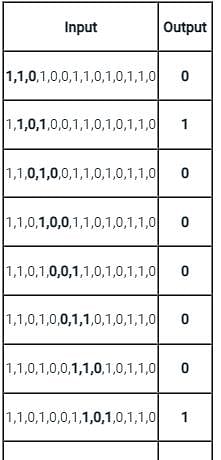

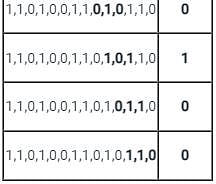

A sequence detector is designed to detect precisely 3 digital inputs, with overlapping sequences detectable. For the sequence (1,0,1) and input data (1,1,0,1,0,0,1,1,0,1,0,1,1,0), what is the output of this detector?

|

6 videos|76 docs|52 tests

|

|

6 videos|76 docs|52 tests

|