Test: Addressing Modes- 2 - Computer Science Engineering (CSE) MCQ

15 Questions MCQ Test GATE Computer Science Engineering(CSE) 2025 Mock Test Series - Test: Addressing Modes- 2

Consider a high-level language statement while [* i - -] then which addressing mode is suitable for it?

Given below are some statements associated with the registers of a CPU. Identify the false statement.

| 1 Crore+ students have signed up on EduRev. Have you? Download the App |

Which of the following is not valid class of interrupts?

1. Program

2. Timer

3. I/O

4. Hardware failure

System calls are usually invoked by using

1. An indirect jump

2. A software interrupt

3. Polling

4. A privileged instruction

Microinstruction length is determined by _____.

1. The maximum number of simultaneous micro operations that must be specified.

2. The way in which the control information is represented or encoded.

3. The way in which the next microinstruction address is specified.

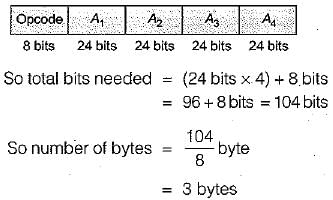

In four-address instruction format, the number of bytes required to encode an instruction is (assume each address requires 24 bits, and 1 byte is required for operation code)

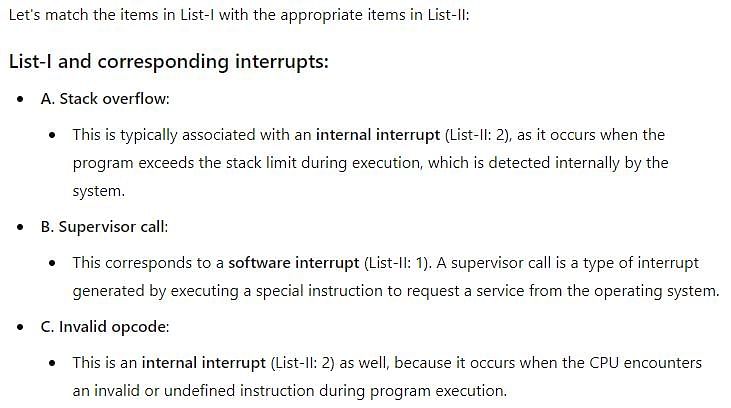

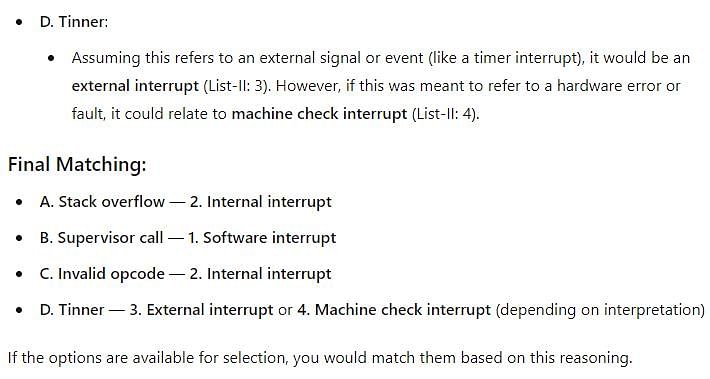

Match List-I with List-ll and select the correct answer using the codes given below the lists:

List-I

A. Stack overflow

B. Supervisor call

C. Invalid opcode

D. Tinner

List-ll

1. Software interrupt

2. Internal interrupt

3. External interrupt

4. Machine check interrupt

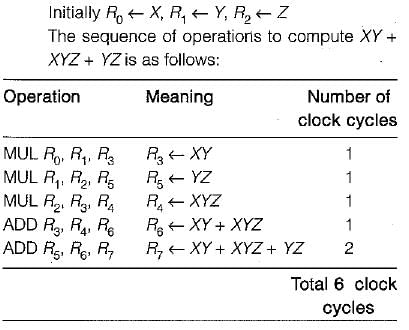

Consider a CPU has 8 general-purpose registers

R0, R1..., R7 and supports the following operations.

ADD Ra, Rb, Rc Add Ra to Rb and store the result to Rc.

MUL Ra, Rb, Rc Multiply Ra to Rb and store the result to Rc.

An operation normally takes one clock cycles, an operation takes two clock cycles if it produces a result required by the immediately following operations. Consider the expression XY + XYZ + YZ, where variables X, Y and Z are initially located in the registers R0, R1 and R2. If contents these registers must not be modified, what is the minimum number of clock cycles required for an operation sequence that computes the value of XY + XYZ + YZ?

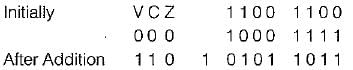

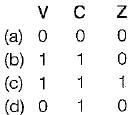

A CPU has an arithmetic unit that adds bytes and then sets its V, C and Z flag bits as follows. The V-bit is set if arithmetic overflow occurs (in 2’s complement arithmetic). The C-bit is set if a carry-out is generated from the most significant bit during an operation. The Z-bit is set if the result is zero. What are the values of the V, C and Z flag bit after 8-bit byte 1100 1100 and 10001111 are added?

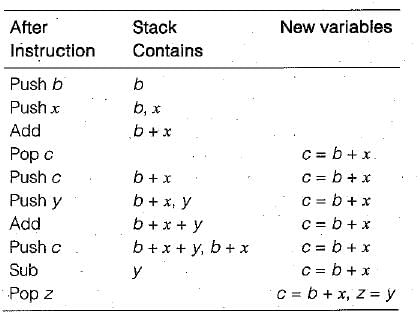

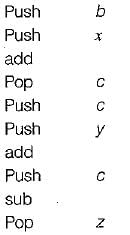

Consider the following sequence of instructions intended for execution on a stack machine. Each arithmetic operation pops the second operand, then pops the first operand, operates on them, and then pushes-the result back onto the stack

Which of the following statements is/are true?

1. If push and pop instructions each require 5 bytes of storage, and arithmetic operations each require 1 byte of storage then the instruction sequence as a whole requires a total of 40 bytes of storage.

2. At the end of execution, zcontainsthe same value as y.

3. At the end of execution, the stack is empty.

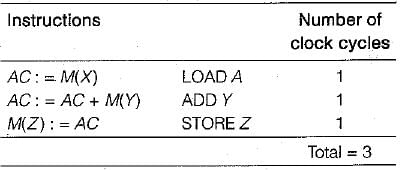

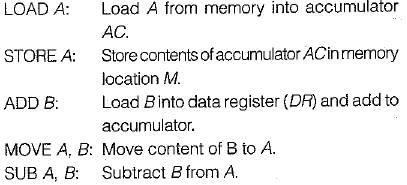

Consider an accumulator-based CPU supports only single address instruction. The CPU supports the following instructions:

Assume CPU uses the memory referencing and each instruction LOAD, STORE and ADD takes one clock cycle. To compute Z = X + Y CPU takes how many minimum number of clock cycles?

|

55 docs|215 tests

|

|

55 docs|215 tests

|