Test: Synchronous & Asynchronous Circuits - Computer Science Engineering (CSE) MCQ

10 Questions MCQ Test GATE Computer Science Engineering(CSE) 2025 Mock Test Series - Test: Synchronous & Asynchronous Circuits

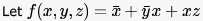

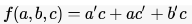

be a switching function. Which one of the following is valid?

be a switching function. Which one of the following is valid?

Which are the essential prime implicants of the following Boolean function?

| 1 Crore+ students have signed up on EduRev. Have you? Download the App |

A main memory unit with a capacity of 4 megabytes is built using 1M x 1-bit DRAM chips. Each DRAM chip has 1K rows of cells with 1K cells in each row. The time taken for a single refresh operation is 100 nanoseconds. The time required to perform one refresh operation on all the cells in the memory unit is

A ROM is used to store the Truth table for a binary multiple unit that will multiply two 4-bit numbers. The size of the ROM that is required to accommodate the Truth table is

. Write the values of M and N.

A ROM is used to store the table for multiplication of two 8-bit unsigned integers. The size of ROM required is

What is the minimum size of ROM required to store the complete truth table of multiplier?

The amount of ROM needed to implement a 4 - bit multiplier is

Which of the following input sequences for a cross-coupled R-S flip-flop realized with two NAND gates may lead to an oscillation?

The below figure shows four D-type flip-flops connnected as a shift register using an XOR gate. The initial state and three subsequent states for three clock pulses are also given.

The state after the fourth clock pulse is

Consider the circuit given below with initial state . The state of the circuit is given by the value

Which one of the following is correct state sequence of the circuit?

|

55 docs|215 tests

|

|

55 docs|215 tests

|