Test: Cache Memory- 2 - SSC CGL MCQ

30 Questions MCQ Test SSC CGL Tier 2 - Study Material, Online Tests, Previous Year - Test: Cache Memory- 2

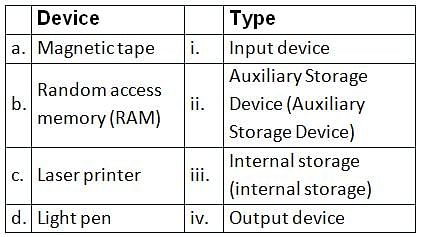

Which of the following is NOT a part of auxiliary memories in a Computer system?

| 1 Crore+ students have signed up on EduRev. Have you? Download the App |

Which one of the following memory units is considered as the largest?

Which of the following memory devices is very much similar, mainly in terms of speed, to the cache memory?

Which among the following memories is used in Digital camera?

Which of the following is a Permanent Memory in the computer?

Which memory cannot be accessed directly by the CPU of the computer?

The actual timing signals that govern the transfer of data between input unit, processor, memory and output units are generated by the ________ and the ______ stores the processed data.

The primary memory (also called main memory) of a personal computer consists of

The Boot sector files of the system are stored in which computer memory?

Which of the following has the fastest speed in the computer memory hierarchy?

Which process is used to map logical addresses of variable length onto physical memory?

Which computer memory chip allows simultaneous both read and write operations?

In which type of memory, once the program or data is written, it cannot be changed?

Which of the following statements are not correct about the main memory of a computer?

|

1365 videos|1312 docs|1010 tests

|

|

1365 videos|1312 docs|1010 tests

|