Test: Control Unit- 2 - Computer Science Engineering (CSE) MCQ

15 Questions MCQ Test GATE Computer Science Engineering(CSE) 2025 Mock Test Series - Test: Control Unit- 2

Which set of instruction transfers the memory word specified by the effective address to AC or Load to AC?

Which of the following is not involved in a memory write operation?

| 1 Crore+ students have signed up on EduRev. Have you? Download the App |

In Flynn’s classification of computers, the vector and array classes of machines belong to

Following are some statements associated with microprocessors. Identify the false statement.

The following are four statements regarding what a CPU with only a set of 32 bit registers can perform.

1. Hold and operate on 32 bit integers.

2. Hold and operate on 16 bit integers.

3. Hold and operate on 64 bit floating point arithmetic.

4. Hold and operate on 16 bit UNICODE characters.

Which of the following is true about such a CPU?

The following are four statements about Reduced Instruction Set Computer (RISC) architectures.

1. The typical RISC machine instruction set is small, and is usually a subject of a CISC instruction set.

2. No arithmetic or logical instruction can refer to the memory directly.

3. A comparatively large number of user registers are available.

4. Instructions can be easily decoded through hard-wired control units.

Which of the above statements is true?

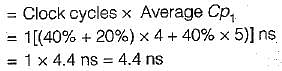

Consider an unpipelined processor assume that it has a 1 ns clock cycles and that it uses 4 cycles for ALU operation and branches and 5 cycles for memory operations. Assume that the relative frequencies of these operations are 40%, 20% and 40% respectively. Suppose due to clock skew and setup, pipelining the processor adds 0.2 ns of overhead to the clock, ignore any latency impact.

Q. What is the average instruction execution time for unpipelined processor?

Consider an unpipelined processor assume that it has a 1 ns clock cycles and that it uses 4 cycles for ALU operation and branches and 5 cycles for memory operations. Assume that the relative frequencies of these operations are 40%, 20% and 40% respectively. Suppose due to clock skew and setup, pipelining the processor adds 0.2 ns of overhead to the clock, ignore any latency impact.

Q. What speedup gain after pipelined the processor?

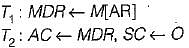

The following are the some of the sequences of operations in instruction cycle, which one is correct sequence?

Consider the following situation and fill in the blanks:

The computer starts the tape moving by issuing a command: the processor then monitors the status of the tape by means of a _____. When the tape is in the correct position, the processor issues a _______.

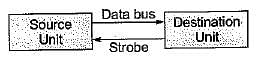

Asynchronous data transfer between two independent units requires that control signals be transmitted between the communicating units to indicate the time at which data is being transm itted, way of achieving this ______.

Determine the width of Micro-instruction having following Control signal field, in a Vertical Microprogrammed Control Unit

1. Next Address field of 7 Bits

2. ALU Function field selecting 1 out of 13 ALU Function.

3. Register-in field selecting 1 out of 13 ALU Function.

4. Register-out field selecting 1 out of 8 registers.

5. Shifter field selecting no shift, right shift or left shift.

6. Auxiliary control field of 4 bits.

The disadvantage of hard-wired control units with flip-flops is ______.

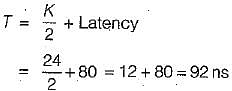

A CPU has a cache with block size 64 bytes. The main memory has k blocks, each block being c bytes wide. Consecutive c-byte chunks are mapped on consecutive blocks with warp-around. All the k blocks can be accessed in parallel, but two accesses to the same block must be serialized. A cache block access may involve multiple iterations of parallel block accesses depending on the amount of data obtained by accessing all the k-blocks in parallel. Each iteration requires decoding the block numbers to be accessed in parallel and this takes k/2 ns.

The latency of one block access is 80 ns. If c = 2 and k = 24, then latency of retrieving a cache block starting at address zero from main memory is

|

55 docs|215 tests

|

|

55 docs|215 tests

|