Test: Combinational Circuit- 2 - Computer Science Engineering (CSE) MCQ

15 Questions MCQ Test GATE Computer Science Engineering(CSE) 2025 Mock Test Series - Test: Combinational Circuit- 2

| 1 Crore+ students have signed up on EduRev. Have you? Download the App |

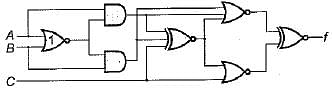

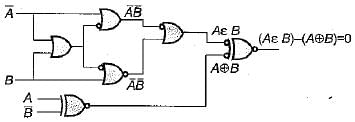

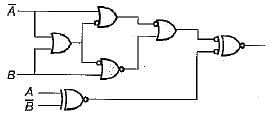

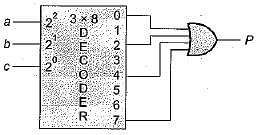

The output of the circuit shown in following figure is equal to

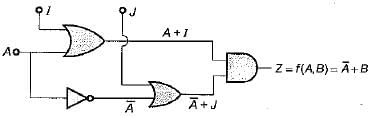

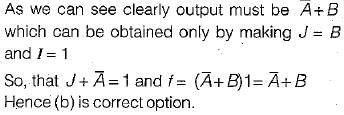

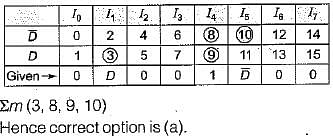

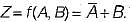

The circuit given in figure is to be used to implement the function  What is the values should be selected I and J?

What is the values should be selected I and J?

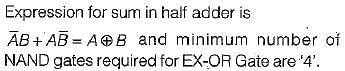

Minimum number of NAND gates required to implement sum in half-adder circuit is:

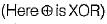

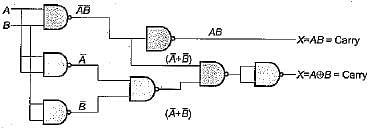

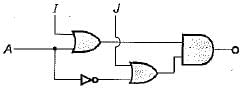

The following circuit is an implemented of:

1. Sum of full adder

2. Carry of half adder

3. Difference of full subtracte

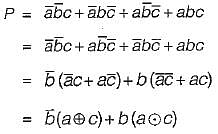

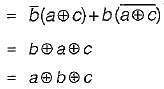

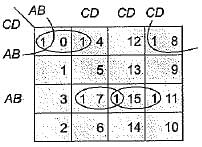

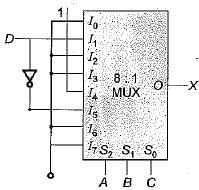

The circuit below represents function X{A, B, C, D) as:

If half adders and full adders are implemented using gates, then for the addition of two 17 bit numbers (using minimum gates) the number of half adders and full adders required will be

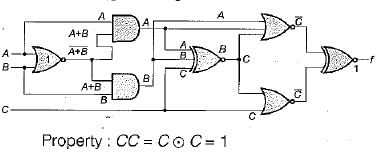

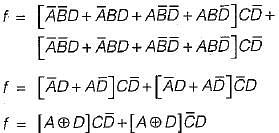

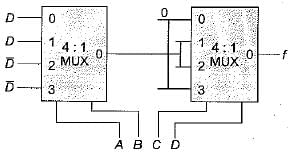

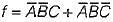

To realize following function 'f'

How many minimum number of 2 input NAND gates are required

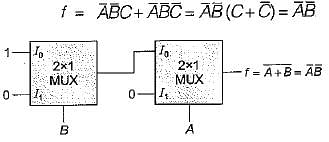

Minimum number of 2 x 1 multiplexers required to realize the following function,  Assume that inputs are available only in true forr and Boolean constants.1 and 0 are available.

Assume that inputs are available only in true forr and Boolean constants.1 and 0 are available.

The number of full and half-adder required to add 16-bit numbers is

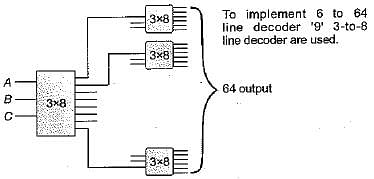

How many 3-to-8 line decoders with an enable input are needed to construct a 6-to-64 line decoder without using any other logic gates?

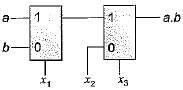

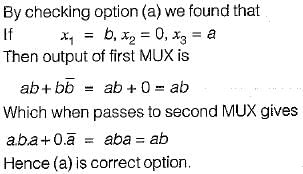

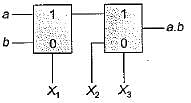

The following circuit implements a two-input AND gate using two 2-1 multiplexers.

What are the values of X1 X2, X3?

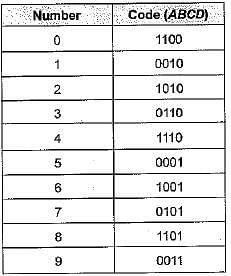

Consider excess-3 code that is used to represent integers 0 through 9 as shown below:

Which of the following expressions is the correct one for an invalid code?

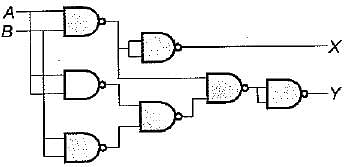

What logic function is performed by the circuit shown below:

|

55 docs|215 tests

|

|

55 docs|215 tests

|