Test: Digital Electronics - 4 - Electrical Engineering (EE) MCQ

25 Questions MCQ Test Digital Electronics - Test: Digital Electronics - 4

For an N bit ADC, the percentage resolution is [1/2N - 1)] 100.

| 1 Crore+ students have signed up on EduRev. Have you? Download the App |

Commercial ECL gates use two ground lines and one negative supply to

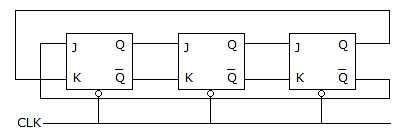

A 3 stage Johnson counter (ring) shown in figure is clocked at a constant frequency of fc from the starting state of Q0 Q1 Q2 = 101. The frequency of output Q0 Q1 Q2 will be

A depletion type NMOS is operated in enhancement mode. Vp = - 4 volts. For VGS = + 3 volts as VDS is increased, ID becomes nearly constant when Vps equals

A number is expressed in binary 2's complement as 10011 decimal equivalent value is

Which one of the following is D/A conversion technique?

Assuming accumulator contain A 64 and the carry is set (1). What will accumulator (A) and carry (CY) contain after ANA A?

The product of which of the following gives the figure of merit of a logic family?

In a 4 bit parallel in parallel out shift register A = 1, B = 1, C = 0, D = 1. The data output after 3 clock pulses is

Assertion (A): A 4 input variable logic circuit can be implemented using a 8 : 1 multiplexer.

Reason (R): When a multiplexer is used as a logic function generator, the logic design is simple.

A 6 MHz channel is used by a digital signalling system initializing four-level signals. The maximum possible transmission rate is

Data can be changed from spatial code to temporal code and vice-versa by using

In 8156, the lower times byte is addressed with 24 H, and the upper times byte with

Which one of the following is used to change data from spatial code to temporal code?

Which of the following needs DC forward voltage to emit light?

If a microcomputer has a 64 K memory; what is the hexadecimal notations for the last memory location?

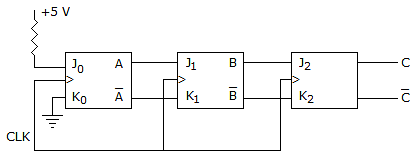

In the given figure shows a 3 bit shift register using TTL flip flops. Initially all the flip flops are set to 0 state. After 8 clock pulses

|

115 videos|71 docs|58 tests

|

|

115 videos|71 docs|58 tests

|