Test: Sample & Hold Circuits - Electrical Engineering (EE) MCQ

10 Questions MCQ Test Analog and Digital Electronics - Test: Sample & Hold Circuits

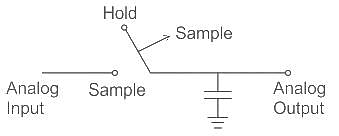

A good Sample and Hold circuit should have

- High input impedance

- High output impedance

- Low input impedance

- Low output impedance

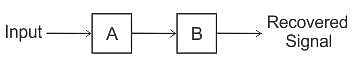

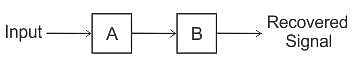

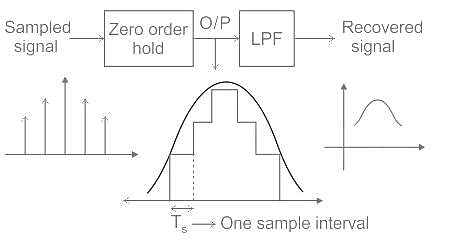

Figure shows 4 block diagram of a system to recover a sampled signal shown as input.

Blocks A and B can be respectively :

Blocks A and B can be respectively :

| 1 Crore+ students have signed up on EduRev. Have you? Download the App |

For a given sample-and-hold circuit, if the value of the hold capacitor is increased, then

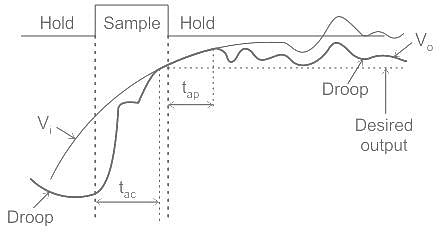

A signal channel signal acquisition system with 0-10 V range consist of a sample and hold circuit with worst case drop rate of 100 μV/ms and 10 bit ADC. The maximum conversion time for the ADC is

When a time-varying signal has to be digitized using an ADC, which of the following is necessary to use before digitization?

The time required to complete the conversion of Analog to Digital is ________ the duration of the hold mode of S/H.

In A/D converter, what is the time relation between sampling period T and the duration of the sample mode and the hold mode?

|

137 videos|143 docs|71 tests

|

|

137 videos|143 docs|71 tests

|

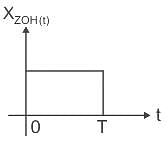

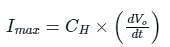

when V0 is the voltage at the steady state.

when V0 is the voltage at the steady state.