Previous Year Questions: Addressing Modes | Computer Architecture & Organisation (CAO) - Computer Science Engineering (CSE) PDF Download

Q1: A stack organized computer is characterised by instructions with (2020)

(a) indirect addressing

(b) direct addressing

(c) zero addressing

(d) index addressing

Ans: (c)

Sol: ACCUMULATOR based instruction ,onthe other hand uses ONE address instruction means that one address is always implied as the ACCUMULATOR.

Hence the option C is correct.

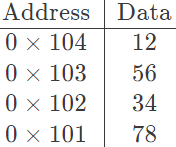

Q2: An array of 2 two byte integers is stored in big endian machine in byte addresses as shown below. What will be its storage pattern in little endian machine ? (2020) (a)

(a)  (b)

(b)  (c)

(c)  (d)

(d)  Ans: (c)

Ans: (c)

Sol: In Big endian, the Most significant byte within the word is stored first(at lower address).

In Little endian, the Least significant byte within the word is stored first(at lower address).

So, if word size is 1 Byte, then little-endian and Big-endian have no difference. Data will be stored in the same way in both of them.

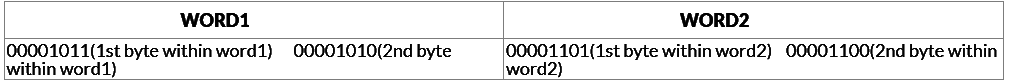

If word size is 2Bytes and this is how 10,11,12,13 are stored in big endian:- Then this is how it will be stored in little endian:-

Then this is how it will be stored in little endian:-

In question, there are two words in the array. Each word has two Bytes. In little and big endian , these bytes within the word will be reverse of each other.

first byte of word1 is 12 and second byte of word1 is 34. So in little endian, first byte of word1 will have 34 and second byte of word1 will have 12.

first byte of word2 is 56 and second byte of word2 is 78. So in little endian, first byte of word1 will have 78 and second byte will have 56.

So, answer is option (C).

Q3: The immediate addressing mode can be used for

1. Loading internal registers with initial values

2. Perform arithmetic or logical operation on data contained in instructions

Which of the following is true? (2020)

(a) Only 1

(b) Only 2

(c) Both 1 and 2

(d) Immediate mode refers to data in cache

Ans: (c)

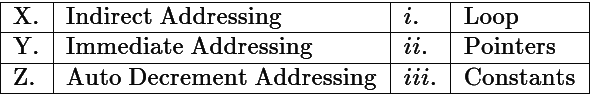

Q4: The most appropriate matching for the following pairs: (2017) (a) X-iii, Y-ii, Z-i

(a) X-iii, Y-ii, Z-i

(b) X-ii, Y-iii, Z-i

(c) X-iii, Y-i, Z-ii

(d) X-ii, Y-i, Z-iii

Ans: (b)

Sol: X: Indirect Addressing - Pointers

Y: Immediate Addressing - Constants

Z: Auto Decrement Addressing - Loop

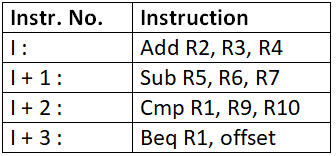

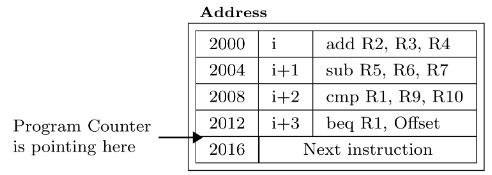

Q5: Consider a RISC machine where each instruction is exactly 4 bytes long. Conditional and unconditional branch instructions use PC- relative addressing mode with Offset specified in bytes to the target location of the branch instruction. Further the Offset is always with respect to the address of the next instruction in the program sequence. Consider the following instruction sequence. If the target of the branch instruction is i, then the decimal value of the Offset is __________ (2017 Set-1)

If the target of the branch instruction is i, then the decimal value of the Offset is __________ (2017 Set-1)

(a) -16

(b) -12

(c) -8

(d) 16

Ans: (a)

Sol: Program Counter is updated with the address of next instruction even before the current instruction is executed.

That is why the question says that the address of the next instruction is updated with next instruction in sequence.

Before executing instruction i + 3, the current state looks as under:

Please note: BEQ instruction is for Branch Equal Question says that the target of branch instruction is 'i' which is at 2000 in our example.

Question says that the target of branch instruction is 'i' which is at 2000 in our example.

So, we need to go to address 2000 from address 2016 (which is currently pointed by PC)

2016−2000 = 16

So, we have to specify Offset as −16 which would mean that 16 should be subtracted from next address instruction (2016).

Q6: Consider the C struct defined below:

struct data {

int marks [100] ;

char grade;

int cnumber;

};

struct data student;

The base address of student is available in register R1. The field student.grade can be accessed efficiently using (2017 SET-1)

(a) Post-increment addressing mode. (R1)+

(b) Pre-decrement addressing mode, -(R1)

(c) Register direct addressing mode, R1

(d) Index addressing mode, X(R1), where X is an offset represented in 2's complement 16-bit representation

Ans: (d)

Sol: Displacement Mode :-

Similar to index mode, except instead of a index register a base register will be used. Base register contains a pointer to a memory location. An integer (constant) is also referred to as a displacement. The address of the operand is obtained by adding the contents of the base register plus the constant. The difference between index mode and displacement mode is in the number of bits used to represent the constant. When the constant is represented a number of bits to access the memory, then we have index mode. Index mode is more appropriate for array accessing; displacement mode is more appropriate for structure (records) accessing.

Q7: Relative mode of addressing is most relevant to writing: (2016)

(a) Co - routines

(b) Position - independent code

(c) Shareable code

(d) Interrupt Handlers

Ans: (b)

Sol: Relative mode addressing is most relevant to writing a position-independent code.

Q8: For computers based on three-address instruction formats, each address field can be used to specify which of the following: (2015 SET-1)

(S1) A memory operand

(S2) A processor register

(S3) An implied accumulator register

(a) Either S1 or S2

(b) Either S2 or S3

(c) Only S2 and S3

(d) All of S1, S2 and S3

Ans: (a)

Sol: Computer with three addresses instruction format can use each address field to specify either processor register or memory operand.

e.g., X = (A+B)∗(C+A)

Equivalent Three address Instructions The advantage of the three address formats is that it results in short program when evaluating arithmetic expression. The disadvantage is that the binary-coded instructions require too many bits to specify three addresses.

The advantage of the three address formats is that it results in short program when evaluating arithmetic expression. The disadvantage is that the binary-coded instructions require too many bits to specify three addresses.

Q9: MOV [BX], AL type of data addressing is called ? (2011)

(a) register

(b) immediate

(c) register indirect

(d) register relative

Ans: (c)

Sol: MOV [BX], AL

move the contents of AL to memory location whose address is in BX (source and target can be either way as per the IA, lets assume first is destination here)

say [BX] = 200

so AL contents are moved to memory location 200

it is example of register indirect.

Q10: Consider a hypothetical processor with an instruction of type LW R1, 20(R2), which during execution reads a 32-bit word from memory and stores it in a 32-bit register R1. The effective address of the memory location is obtained by the addition of constant 20 and the contents of register R2. Which of the following best reflects the Addressing Modes implemented by this instruction for the operand in memory? (2011)

(a) Immediate Addressing

(b) Register Addressing

(c) Register Indirect Scaled Addressing

(d) Base Indexed Addressing

Ans: (d)

Sol: Base Index Addressing, as the content of register R2 will serve as the index, and 20 will be the Base address.

|

20 videos|86 docs|48 tests

|

FAQs on Previous Year Questions: Addressing Modes - Computer Architecture & Organisation (CAO) - Computer Science Engineering (CSE)

| 1. What are the different types of addressing modes in computer science engineering? |  |

| 2. How does immediate addressing mode work in computer science engineering? |  |

| 3. Can you explain direct addressing mode in computer science engineering? |  |

| 4. What is the significance of indirect addressing mode in computer science engineering? |  |

| 5. How is register addressing mode different from other addressing modes in computer science engineering? |  |

|

20 videos|86 docs|48 tests

|

|

Explore Courses for Computer Science Engineering (CSE) exam

|

|