Previous Year Questions: Machine Instruction | Computer Architecture & Organisation (CAO) - Computer Science Engineering (CSE) PDF Download

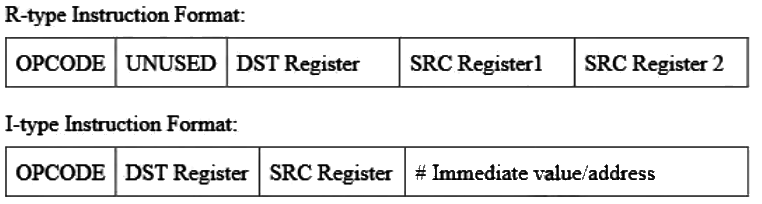

Q1: A processor uses a 32-bit instruction format and supports byte-addressable memory access. The ISA of the processor has 150 distinct instructions. The instructions are equally divided into two types, namely R-type and I-type, whose formats are shown below.

In the OPCODE, 1 bit is used to distinguish between I-type and R-type instructions and the remaining bits indicate the operation. The processor has 50 architectural registers, and all register fields in the instructions are of equal size.

Let X be the number of bits used to encode the UNUSED field, Y be the number of bits used to encode the OPCODE field, and Z be the number of bits used to encode the immediate value/address field. The value of X + 2Y + Z is ______ (2024 SET-2)

(a) 34

(b) 56

(c) 42

(d) 64

Ans: (a)

Sol: Opcode field(Y): There are 150 instructions, and they are equally divided into two types. Therefore, there are 75 I-type instructions and 75 R-type instructions. Since one bit is used to distinguish between instruction types, the number of bits used to encode opcode field is Y = (1+7) = 8

Register field: There are 50 architectural registers and all register fields in the instructions are of equal size. Therefore, the number of bits used to encode register field is 6

Unused field(X): The number of bits used to encode unused field in R-type instructions is X = 32 - (8 + 6 + 6 + 6) = 6

Immediate value/address field(Z): The number of bits used to encode immediate value/address field in I-type instructions is Z = 32 - (8 + 6 + 6) = 12

Therefore, the values of X, Y, and Z are:

- X = 6 bits (UNUSED field)

- Y = 8 bits (OPCODE field)

- Z = 12 bits (immediate value/address field)

So the answer is 6 + 2 * 8 + 12 = 34

Q2: A processor with 16 general purpose registers uses a 32-bit instruction format. The instruction format consists of an opcode field, an addressing mode field, two register operand fields, and a 16-bit scalar field. If 8 addressing modes are to be supported, the maximum number of unique opcodes possible for every addressing mode is _________ (2024 SET-2)

(a) 16

(b) 32

(c) 64

(d) 128

Ans: (b)

Sol: Instruction size = 32 bits

Given that no. of Registers = 16

So no. of bits needed to specify a register in instruction = 4

Given that no. of Addressing modes = 8

So no. of bits needed to specify an addressing mode in instruction = 3

No. of bits available for opcode = Instruction size - (Addressing mode field size + 2 * Register field size + Scalar field size)

= 32 - (3 + 2*4 + 16)

= 32 - 27

= 5

So maximum no. of unique opcodes possible = 25 = 32

Q3: Consider the given C-code and its corresponding assembly code, with a few operands U1-U4 being unknown. Some useful information as well as the semantics of each unique assembly instruction is annotated as inline comments in the code. The memory is byte-addressable. Which one of the following options is a CORRECT replacement for operands in the position (U1, U2, U3, U4) in the above assembly code? (2023)

Which one of the following options is a CORRECT replacement for operands in the position (U1, U2, U3, U4) in the above assembly code? (2023)

(a) (8, 4, 1, Lo2)

(b) (3, 4, 4, Lo1)

(c) (8, 1, 1, Lo2)

(d) (3, 1, 1, Lo1)

Ans: (b)

Sol: To understand u1, we must first find out what the register r5 is storing.

If you check closely the line L02, it’s fetching an element from array b and storing it in r5.

Line L04 is storing the value present in r5 to array a, so we’re definitely performing the multiplication by 8 in L03.

L03 is a shift-left operator. To multiply by 8, how many bits (in binary) do we need to shift to left? If you can find out that number, that would be the answer to u1.

L05 and L06 are incrementing the values of registers r3 and r5 respectively to point to next element of a and b respectively. But by how much shall we increase it to make it point to next element?

Suppose at some point in time, r3 is storing 1000 in decimal and pointing to 2nd element of array a. Recall that each element is 4Bytes in size (given in question). Now, what is the address of 3rd element of array a, can you guess? Yes, it would be 1004. Hence, 4 must be added.

Note: Given memory is byte addressable. Each int takes 32bit = 4B, so we need to shift by 4 addresses.

u4 should be the line to make the loop repeat. Note that if we make it L02, the loop termination condition is skipped and would lead to infinite loop (or unless we got trapped due to accessing illegal memory).

The value of u1, u2, u3, u4 will be 3, 4, 4, L01.

Option B is the right answer.

Q4: Consider the following instruction sequence where registers R1, R2 and R3 are general purpose and MEMORY [X] denotes the content at the memory location X. Assume that the content of the memory location 5000 is 10, and the content of the register R3 is 3000. The content of each of the memory locations from 3000 to 3020 is 50. The instruction sequence starts from the memory location 1000. All the numbers are in decimal format. Assume that the memory is byte addressable.

Assume that the content of the memory location 5000 is 10, and the content of the register R3 is 3000. The content of each of the memory locations from 3000 to 3020 is 50. The instruction sequence starts from the memory location 1000. All the numbers are in decimal format. Assume that the memory is byte addressable.

After the execution of the program, the content of memory location 3010 is ____________. (2021 SET-1)

(a) 50

(b) 100

(c) 60

(d) 110

Ans: (a)

Sol: The given code is iterating 10 times and incrementing the contents of locations

So, correct answer: 50.

Q5: A computer which issues instructions in order, has only 2 registers and 3 opcodes ADD, SUB and MOV. Consider 2 different implementations of the following basic block : Assume that all operands are initially in memory. Final value of computation also has to reside in memory. Which one is better in terms of memory accesses and by how many MOV instructions? (2020)

Assume that all operands are initially in memory. Final value of computation also has to reside in memory. Which one is better in terms of memory accesses and by how many MOV instructions? (2020)

(a) Case 2, 2

(b) Case 2, 3

(c) Case 1, 2

(d) Case 1, 3

Ans: (a)

Q6: Consider a 32- bit processor which supports 70 instructions. Each instruction is 32 bit long and has 4 fields namely opcode, two register identifiers and an immediate operand of unsigned integer type. Maximum value of the immediate operand that can be supported by the processor is 8191. How many registers the processor has? (2020)

(a) 32

(b) 64

(c) 128

(d) 16

Ans: (b)

Sol:

Number of instructions which are supported = 70

13 - bits support the maximum value of immediate operand = 8191

Now,

Number of bits needed for opcode = 7 bits

Number of bits left to represent register bits = 12

which means 6 - bits per register.

Hence, at max. 64 registers.

∴ (b) is the correct option.

Q7: A non-pipelined CPU has 12 general purpose registers?(R0, R1, R2,..., R12). Following operations are supported

ADD Ra, Rb, Rr Add Ra to Rb and store the result in Rr

MUL Ra, Rb, Rr Multiply Ra to Rb and store the result in Rr

MUL operation takes two clock cycles, ADD takes one clock cycle.

Calculate minimum number of clock cycles required to compute the value of the expression XY + XYZ + YZ. The variable X, Y, Z are initially available in registers R0, R1 and R2 and contents of these registers must not be modified. (2020)

(a) 5

(b) 6

(c) 7

(d) 8

Ans: (b)

Sol: Let's first rewrite the expression as: y*(x + z + x*z)

the instructions are:

ADD R0, R1, R3

MUL R0, R1, R4

ADD R3, R4, R3

MUL R2, R3, R3

Since it is a non-pipelined processor it will take 2*2 + 2*1 = 6 cycles

Q8: Statements associated with registers of a CPU are given. Identify the false statement. (2020)

(a) The program counter holds the memory address of the instruction in execution

(b) Only opcode is transferred to the control unit

(c) An instruction in the instruction register consists of the opcode and the operand

(d) The value of the program counter is incremented by 1 once its value has been read to the memory address register

Ans: (a)

Sol: C holds the address of the next instruction to be fetched.

MAR holds the address of the instruction being executed.

So, A is False (Answer)

Control Unit needs only the Opcode field of the instruction. The other information (Addressing Mode, and the Operands) are required by the ALU to perform the involved computation.

So, B is True.

Instruction Register (IR) is the register that holds the instruction itself (NOT the address of it).

We say an instruction is fetched when we successfully load it in the IR. Of course, it will consist of the Opcode and the Operands.

So, C is True.

Memory Address Register (MAR) holds the address of the current instruction in execution. When the contents of PC are loaded into MAR, PC is incremented where the next instruction is.

Iff the size of an instruction is 1 word, only then PC would be incremented by 1.

Option D is True under this assumption.

Q9: A processor has 64 registers and uses 16-bit instruction format. It has two types of instructions: I-type and R-type. Each I-type instruction contains an opcode, a register name, and a 4-bit immediate value. Each R-type instruction contains an opcode and two register names. If there are 8 distinct I-type opcodes, then the maximum number of distinct R-type opcodes is _______. (2020)

(a) 16

(b) 8

(c) 14

(d) 12

Ans: (c)

Sol: Instruction Length: 16 bits

To distinguish among 64 registers, we need log2(64) = 6 bits

I-type instruction format: R-type instruction format:

R-type instruction format: Maximum possible encodings = 216

Maximum possible encodings = 216

It is given that there are 8 I-type instructions. Let's assume the maximum R-type instructions to be x.

Therefore, (8 × 26 × 24) + (x × 26 × 26) = 216

⇒ x = 16−2 = 14

Q10: Consider the following data path diagram. Consider an instruction: R0 ← R1 + R2. The following steps are used to execute it over the given data path. Assume that PC is incremented appropriately. The subscripts r and w indicate read and write operations, respectively.

Consider an instruction: R0 ← R1 + R2. The following steps are used to execute it over the given data path. Assume that PC is incremented appropriately. The subscripts r and w indicate read and write operations, respectively.

1.R2r, TEMP1r, ALUadd, TEMP2w

2.R1r, TEMP1w

3.PCr, MARw, MEMr

4.TEMP2r, R0w

5.MDRr, IRw

Which one of the following is the correct order of execution of the above steps? (2020)

(a) 2,1,4,5,3

(b) 1,2,4,3,5

(c) 3,5,2,1,4

(d) 3,5,1,2,4

Ans: (c)

Sol: 3rd followed by 5th are Instruction fetch cycle micro operations and can be elaborated as follows:

t1:MARw←PCr

t2:MDRw←Memoryr∣PC←PC+1

t3:IRw←MDRr

Now we need to perform Execute cycle micro operations. Just observe the figure and it will be very easy to identify the sequence between 1st, 2nd, 4th 2nd is clearly stating that we need to move R1 content to some temporary register named as TEMP1 and it is very clear that before performing ALU operation we need the content in TEMP1. Hence 2nd will be performed next after 5th.

2nd is clearly stating that we need to move R1 content to some temporary register named as TEMP1 and it is very clear that before performing ALU operation we need the content in TEMP1. Hence 2nd will be performed next after 5th.

TEMP1w ← R1r

Now we can perform ALU operation and can take second operand directly from R2 and the figure clearly shows us that we need to put the result of ALU back into TEMP2. All these steps are performed in 1st. So 1st will be next.

TEMP2w ← TEMP1r + ALUadd R2r

Lastly we need to put the result present in TEMP2 into R0. This step is performed by 4th.

R0w ← TEMP2r

Correct Answer (C) : 3, 5, 2, 1, 4

Q11: A byte addressable computer has a memory capacity of 2mKB(k bytes ) and can perform 2n operations. An instruction involving 3 operands and one operator needs maximum of: (2018)

(a) 3m bits

(b) 3m+n bits

(c) m+n bits

(d) none of the above

Ans: (d)

Sol: Memory capacity = 2mKB = 2m+10B

Since byte addressable memory is given 1 word = 1 byte

Memory capacity = 2m+10 words

No. of bits required to point 1 memory location = m+10 bits

Total no. of operations = 2n

No. of bits to define 1 operation = n bits

Given an instruction have 3 operands and 1operator.

No. of bits needed by instructions = 3∗(m+10)+n

= 3m+n+30 bits

Option (d) is the correct answer.

Q12: A data driven machine is one that executes an instruction if the needed data is available. The physical ordering of the code listing does not dictate the course of execution. Consider the following pseudo-code:

A. Multiply E by 0.5 to get F

B. Add A and B to get E

C. Add B with 0.5 to get D

D. Add E and F to get G

E. Add A with 10.5 to get C

Assume A,B,C are already assigned values and the desired output is G. Which of the following sequence of execution is valid? (2018)

(a) B, C, D, A, E

(b) C, B, E, A, D

(c) A, B, C, D, E

(d) E, D, C, B, A

Ans: (b)

Sol: We can give data dependency as follows with each node being the corresponding instruction.

So, instruction A cannot happen before instruction B and also instruction D cannot happen before either instruction A or instruction B. Only option satisfying this is option B.

So, instruction A cannot happen before instruction B and also instruction D cannot happen before either instruction A or instruction B. Only option satisfying this is option B.

Q13: A processor has 16 integer registers (R0, R1,...,R15) and 64 floating point registers (F0, F1,...,F63). It uses a 2-byte instruction format. There are four categories of instructions: Type-1, Type-2, Type-3, and Type-4. Type-1 category consists of four instructions, each with 3 integer register operands (3Rs). Type-2 category consists of eight instructions, each with 2 floating point register operands (2Fs). Type-3 category consists of fourteen instructions, each with one integer register operand and one floating point register operand (1R+1F). Type-4 category consists of N instructions, each with a floating point register operand (1F).

The maximum value of N is __________. (2018)

(a) 8

(b) 16

(c) 32

(d) 64

Ans: (c)

Sol: We have 2-byte instruction format. So, total number of instruction encodings = 216

PS: This is not the number of different instructions but different encodings; a single instruction can have different encodings when the address part differs.

No. of bits taken by an integer operand (16 possible integer registers) = log216 = 4.

No. of bits taken by a floating point operand (64 possible floating point registers) = log264 = 6.

No. of encodings consumed by Type 1 instructions = 4×23×4 = 214.

No. of encodings consumed by Type 2 instructions = 8×22×6 = 215.

No. of encodings consumed by Type 3 instructions = 14×2(4+6) = 14336.

No. of encodings left for Type 4 = 216−(214+215+14336) = 2048.

No. of different instructions of Type 4= 2048/64 = 32.

Q14: Consider the following processor design characteristics.

I. Register-to-register arithmetic operations only

II. Fixed-length instruction format

III. Hardwired control unit

Which of the characteristics above are used in the design of a RISC processor? (2018)

(a) I and II only

(b) II and III only

(c) I and III only

(d) I, II and III

Ans: (d)

Sol: Hardwired control units are implemented through use of combinational logic units, featuring a finite number of gates that can generate specific results based on the instructions that were used to invoke those responses. Their design uses a fixed architecture—it requires changes in the wiring if the instruction set is modified or changed. This architecture is preferred in reduced instruction set computers (RISC) as they use a simpler instruction set.

Instructions length cannot vary in RISC usually it's 32 bit. For CISC it can be between 16 to 64 bits.

The hardwired control unit is used when instructions are fixed.

Register to register operations is always possible in RISC. CISC can have memory to memory instructions also.

Q15: Consider a processor with 64 registers and an instruction set of size twelve. Each instruction has five distinct fields, namely, opcode, two source register identifiers, one destination register identifier, and a twelve-bit immediate value. Each instruction must be stored in memory in byte-aligned fashion. If a program has 100 instructions, the amount of memory(in bytes) consumed by the program text is _____ . (2016 Set-2)

(a) 425

(b) 500

(c) 800

(d) 600

Ans: (b)

Sol: Number of registers = 64

Number of bits to address register = ⌈log264⌉ = 6−bits

Number of Instructions = 12

Opcode size = ⌈log212⌉ = 4

Total bits per instruction = 34

Total bytes per instruction = 4.25

Due to byte alignment we cannot store 4.25 bytes, without wasting 0.75 bytes.

So, total bytes per instruction = 5

Total number of instructions = 100

Total size = Number of instructions × Size of an instruction

= 100 × 5 = 500 bytes

Q16: A processor has 40 distinct instructions and 24 general purpose registers. A 32-bit instruction word has an opcode, two register operands and an immediate operand. The number of bits available for the immediate operand field is _______ . (2016 Set-2)

(a) 14

(b) 16

(c) 18

(d) 20

Ans: (b)

Sol: Instruction Opcode Size = log240 = 6

Register operand size = log224 = 5

Total bits available = 32

Bits required for opcode + two register operands = 6+2×5 = 16

Bits available for immediate operand = 32 - 16 = 16.

Q17: In X=(M+NxO)/(PxQ), how many one-address instructions are required to evaluate it? (2015)

(a) 4

(b) 6

(c) 8

(d) 10

Ans: (c)

Sol: Accumulator CPU is example of One Address Instruction:

In Acc. CPU first alu operand is always required in the accumulator but second alu operand can be in the register or memory because of the the availability of the one address along with the opcode.

Load and Store is One address Instruction

X= (M + N x O)/(P x Q)

I1: Load P : ACC<--M[P] //Load the P value from memory to ACCUMULATOR

I2: Mul Q: ACC<--ACC*M[Q] //Second alu operand is in memory and destination is Register

I3: Store T: M[T]<--ACC //Store the Value in memory

I4: Load N : ACC<--M[N]

I5: Mul O : ACC<--ACC*M[O]

I6: Add M: ACC<--ACC+M[M]

I7: Div T: ACC<--ACC/M[T]

I8: Store X: M[X]<--ACC //Finally store in value in memory

TOTAL 8 1 ADDRESS INSTRUCTION REQUIRED.

Q18: The contents of the flag register after execution of the following program by 8085 microprocessor will be (2015)

Program

SUB A

MVI B,(01)H

DCR B

HLT

(a) (54)H

(b) (00)H

(c) (01)H

(d) (45)H

Ans: (a)

Sol: 8085 microprocessor has a 8 bit flag register to indicate certain conditions arising after arithmetic and logical operations or to control certain operations.

- Carry flag indicates whether there is carry or not after an arithmetic and logical operation.

- Parity flag indicates whether the result contains odd number of 1s or even number of 1s.

- Auxiliary carry (or half carry) flag indicates that is there carry from the 3rd bit to 4th.

- Zero flag indicates whether the result of an arithmetic or logical operation is zero or nonzero.

- Sign flag indicates whether the result is positive or negative.

- Other bits in this register are undefined.

- SUB A: subtracts the content of accumulator (A) from the content of the accumulator (A); Content of A will become (00)H; Flag Register: 0100 0100 because result is zero and result contains 0 (even) number of 1s.

- MVI B, (01)H : stores 01 in register B; No computation, no change in Flag Register.

- DCR B: decreases content of register B; Content of B will become (00)H; Flag Register: 0100 0100 because result is zero and result contains 0 (even) number of 1s and DCR/INC don't affect the carry flag in 8085.

Q19: Consider a processor with byte-addressable memory. Assume that all registers, including Program Counter (PC) and Program Status Word (PSW), are of size 2 bytes. A stack in the main memory is implemented from memory location (0100)16 and it grows upward. The stack pointer (SP) points to the top element of the stack. The current value of SP is (016E)16. The CALL instruction is of two words, the first word is the op-code and the second word is the starting address of the subroutine (one word = 2 bytes). The CALL instruction is implemented as follows:

Store the current value of PC in the stack

Store the value of PSW register in the stack

Load the starting address of the subroutine in PC

The content of PC just before the fetch of a CALL instruction is (5FA0)16. After execution of the CALL instruction, the value of the stack pointer is (2015 Set-2)

(a) (016A)16

(b) (016C)16

(c) (0170)16

(d) (0172)16

Ans: (d)

Sol: First we have to consider here memory is byte-addressable

The CALL instruction is implemented as follows:

- Store the current value of PC in the stack

PC is 2 bytes it means when we store pc in stack it will increase by 2

So current value of SP is (016E)16+2 - Store the value of PSW register in the stack

PSW is 2 byte it means when we store psw in stack it will increase by 2

So current value of SP is (016E)16+2+2 = (0172)16

Q20: Assume that 16-bit CPU is trying to access a double word stating at an odd address. How many memory operations are required to access the data? (2014)

(a) 1

(b) 2

(c) 3

(d) 4

Ans: (c)

Sol: 3 for double word beginning at odd address.

2 for double word beginning at even address.

1 for single word beginning at even address.

2 for single word beginning at odd address.

Q21: Consider two processors P1 and P2 executing the same instruction set. Assume that under identical conditions, for the same input, a program running on P2 takes 25% less time but incurs 20% more CPI (clock cycles per instruction) as compared to the program running on P1. If the clock frequency of P1 is 1GHz, then the clock frequency of P2 (in GHz) is _________. (2014 Set-1)

(a) 3.75

(b) 1.6

(c) 2

(d) 2.6

Ans: (b)

Sol: CPU TIME (T) = No. of Instructions (I) × No. of Cycles Per Instruction (c) × Cycle Time (t)

OR

CPU TIME (T) =  → T = Ic x CPI x F-1

→ T = Ic x CPI x F-1

→  P1 & P2 executing same instruction set So,

P1 & P2 executing same instruction set So,

No. of Instructions same for both = I1 = I2 = I

If P1 takes T1 time,

→ T2 = 0.75 x T1 → T2/T1 = 0.75

If P1 incurs C1 clock cycles per instruction,

→ C2 = 1.2 x C1 → C2/C1 =1.2

Since I is same for both, Hence, the clock frequency of P2 is = 1.6 GHz.

Hence, the clock frequency of P2 is = 1.6 GHz.

Q22: A machine has a 32-bit architecture, with 1-word long instructions. It has 64 registers, each of which is 32 bits long. It needs to support 45 instructions, which have an immediate operand in addition to two register operands. Assuming that the immediate operand is an unsigned integer, the maximum value of the immediate operand is ____________. (2014 SET-1)

(a) 16383

(b) 8191

(c) 32767

(d) 4097

Ans: (a)

Sol: 64 registers means 6 bits (⌈log264⌉ = 6) for a register operand. So, 2 register operands require 12 bits. Now, 45 instructions require another 6 bits for opcode (⌈log245⌉ = 6). So, totally 18 bits. Now we have 32−18 = 14 bits left for the immediate operand. So, the max value will be 214−1 = 16383 (as the operand is unsigned we do not need a sign bit and with 14 bits we can represent from 0 to 214 − 1)

Q23: How many number of times the instruction sequence below will loop before coming out of the loop? (2013)

MOV AL, 00H

A1: INC AL

JNZ A1

(a) 1

(b) 255

(c) 256

(d) Will not come out of the loop.

Ans: (c)

Sol: 256. AL is incremented 1 in each iteration and after 256 increments, it becomes 0 again as AL register is 8 bits.

When AL = 0000 0000 and CY = 1, JNZ will be false. JNZ means jump when previous operation set Zero flag and not jump when previous operation did not set zero flag. So control comes out of loop after 256 iterations.

Q24: In 8086, the jump condition for the instruction JNBE is? (2013)

(a) CF = 0 or ZF = 0

(b) ZF = 0 and SF = 1

(c) CF = 0 and ZF = 0

(d) CF = 0

Ans: (c)

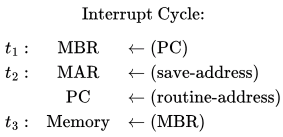

Q25: Consider the following sequence of micro-operations.

MBR ← PC

MAR ← X

PC ← Y

Memory ← MBR

Which one of the following is a possible operation performed by this sequence? (2013)

(a) Instruction fetch

(b) Operand fetch

(c) Conditional branch

(d) Initiation of interrupt service

Ans: (d)

Sol: Here PC value is being stored in memory which is done when either CALL RETURN involved or there is Interrupt. As, we will have to come back to execute current instruction.

So, options (A), (B) are clearly incorrect.

Option (C) is incorrect because conditional branch does not require to save PC contents.

Option (D) is correct as it matches the generic Interrupt Cycle :

Q26: Find the memory address of the next instruction executed by the microprocessor (8086), when operated in real mode for CS=1000 and IP=E000 (2011)

(a) 10E00

(b) 1E000

(c) F000

(d) 1000E

Ans: (b)

Sol: In 8086 the address bus is 20 bit, The address is generated by using segment base and offset.

i.e. Address = segment * 0 x 10 + Offset (Here segment is multiplied by 10h)

Given : Segment base (CS) = 0 x 1000 and Offset (IP) = 0 x E000

Therefore, Address = CS * 0 x 10 + IP

= 0 x 1000*0 x 10 + 0 x E000

= 0 x 1E000

Hence answer is 0 x 1E000 i.e. option B.

|

20 videos|86 docs|48 tests

|

FAQs on Previous Year Questions: Machine Instruction - Computer Architecture & Organisation (CAO) - Computer Science Engineering (CSE)

| 1. What is a machine instruction in computer science? |  |

| 2. How are machine instructions executed by a computer? |  |

| 3. What is the role of machine instructions in programming languages? |  |

| 4. How do machine instructions differ from assembly language instructions? |  |

| 5. Can machine instructions vary between different types of CPUs? |  |

|

20 videos|86 docs|48 tests

|

|

Explore Courses for Computer Science Engineering (CSE) exam

|

|