Static Hazards in Digital Logic

Introduction

A hazard in a digital circuit is a temporary, unintended fluctuation at the output that occurs while the circuit inputs are changing. Hazards arise because different signal paths from inputs to outputs have different propagation delays through gates. As a result, when inputs change, the outputs do not always change simultaneously and may exhibit a brief incorrect value before settling to the intended steady value.

There are three commonly recognised categories of hazards:

- Static hazard

- Dynamic hazard

- Functional hazard

This document discusses static hazards in detail and explains how to detect and remove them using Karnaugh maps (K-maps) and redundant (consensus) terms.

What is a static hazard?

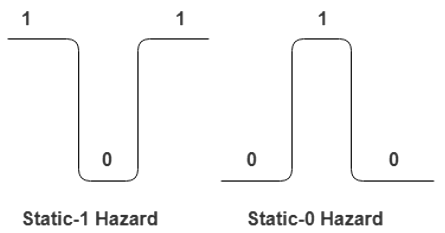

A static hazard occurs when the intended output value remains the same before and after an input change, but the output changes momentarily to the opposite value during the transition and then returns to its correct value. There are two kinds:

- Static-1 hazard: The correct output value is 1. During an input transition the output momentarily falls to 0 and then returns to 1.

- Static-0 hazard: The correct output value is 0. During an input transition the output momentarily rises to 1 and then returns to 0.

Why static hazards occur

Static hazards are caused by unequal delays along different paths that contribute to the same output term. In a sum-of-products (SOP) implementation, two product terms that should cover adjacent minterms may both momentarily evaluate to 0 during a transition because a shared literal changes and the complementary paths do not switch at the exact same times. The missing overlap in the implemented cover (grouping) of minterms in the K-map allows a brief gap in coverage, producing the hazard.

Detecting a static-1 hazard using a K-map

For circuits implemented in SOP form we test for static-1 hazards by examining the K-map of the output function. The usual procedure is:

- Write the Boolean function for the output, call it Y.

- Draw the K-map for Y and mark all cells containing 1.

- Check adjacent 1s (cells that differ by only one variable). If any pair of adjacent 1s are not covered together by a single product-term (prime implicant) in the chosen SOP implementation, that adjacent pair represents a potential static-1 hazard during the transition that moves between those two minterms.

Each such uncovered adjacent pair of 1s corresponds to a transition where the implemented function may produce a momentary 0 even though the true function remains 1.

Example: detection of a static-1 hazard

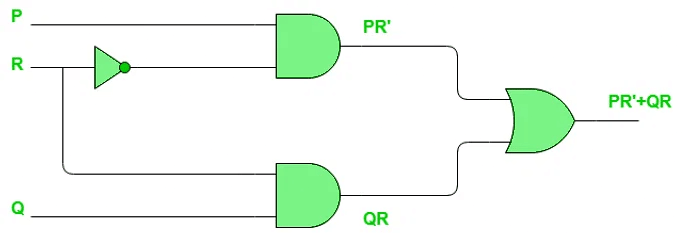

Example - Consider the circuit shown below.

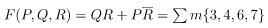

We have the output, call it F, expressed as:

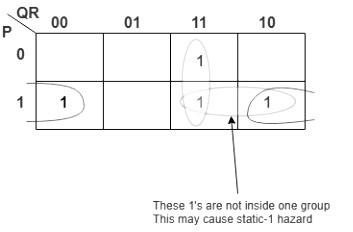

Let us draw the K-map for this Boolean function and examine the grouping of 1s:

In the K-map above, a pair of 1s encircled (green) are adjacent but are not included together in any of the product-term groupings used in the present SOP expression for F. That uncovered adjacent pair is a source of a static-1 hazard; during an input transition that moves between those two minterms, the circuit output may momentarily go to 0.

Removal of a static-1 hazard

To remove a static-1 hazard in an SOP implementation we add a redundant product term (a consensus term) that covers the adjacent pair of 1s which was previously uncovered. Adding this term does not change the final truth table of the function but it fills the coverage gap that allowed the hazard.

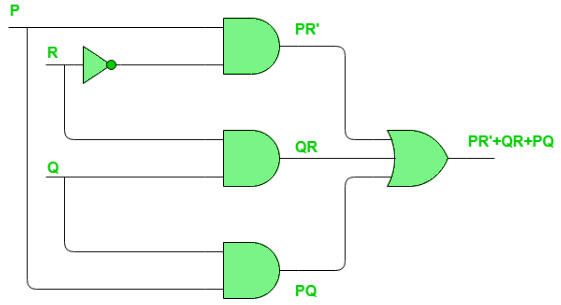

In the example, the pair of 1s causing the hazard is covered by an additional implicant (shown in blue). We include this prime implicant in the SOP expression:

Adding the extra term does not change the set of minterms (the function remains logically equivalent), but it prevents the output from temporarily dropping to 0 during the transition. The resulting circuit (with the redundant gate/term included) is hazard-free for that static-1 case:

Static-0 hazards - detection and removal

Static-0 hazards are dual to static-1 hazards. For circuits implemented in product-of-sums (POS) form:

- Examine the K-map for 0s (instead of 1s).

- If there are adjacent 0 cells that are not grouped together by a single sum term (prime implicate) in the POS implementation, that adjacent pair represents a potential static-0 hazard.

- To remove a static-0 hazard add the redundant sum term (consensus term) that covers the adjacent 0s; this fills the coverage gap without changing the logical function.

In practice, if a function is implemented as SOP but you are concerned about static-0 hazards, you can either convert to an appropriate POS representation that covers 0s properly or add complementary redundancy in the network to prevent transient 1s on a 0 output.

Design guidelines and additional notes

- Static hazards are a property of the implementation (the gate-level network and its grouping) rather than the Boolean function itself. A different implementation of the same function may be hazard-free.

- The usual technique to eliminate static hazards is the inclusion of redundant (consensus) terms so that every adjacent pair of minterms (for static-1) or maxterms (for static-0) is covered by at least one common implicant/implicate.

- When gates have significant and unequal delays, dynamic hazards (multiple unwanted transitions) may also appear; eliminating static hazards reduces the likelihood of dynamic hazards but careful timing-aware design is necessary for full robustness.

- Synthesis tools and careful factoring can produce hazard-reduced or hazard-free implementations; for safety-critical circuits designers explicitly add consensus terms or use hazard-free synthesis techniques.

Conclusion

Static hazards are temporary incorrect outputs caused by unequal path delays when inputs change. They are detected by searching for adjacent minterms (for static-1) or adjacent maxterms (for static-0) that are not jointly covered by a single implicant in the chosen implementation. The standard remedy is to include redundant consensus terms so that every adjacent pair is covered, thereby removing the momentary glitch without changing the logical function.

If you implement or simplify Boolean functions using K-maps, always inspect adjacent 1s (for SOP) or 0s (for POS) and add the necessary redundant terms to ensure reliable operation under real gate delays.

| Explore Courses for Computer Science Engineering (CSE) exam |  |

| Get EduRev Notes directly in your Google search |  |