Previous Year Questions- Microprocessors | Analog and Digital Electronics - Electrical Engineering (EE) PDF Download

Q1: In a given 8-bit general purpose micro-controller there are following flags.

C-Carry, A-Auxiliary Carry, O-Overflow flag, PParity ( 0 for even, 1 for odd) R0 and R1 are the two general purpose registers of the microcontroller.

After execution of the following instructions, the decimal equivalent of the binary sequence of the flag pattern [CAOP] will be (2023)

MOV R0, +0x60

MOV R1, +0x46

ADD R0, R 1

(a) 1

(b) 2

(c) 3

(d) 7

Ans: (b)

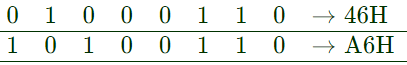

Sol: MOV R0, + 0 × 60 ⇒ R0 ← 60H

MOV R1, + 0 × 46 ⇒ R1 ← 46H

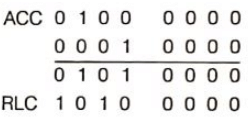

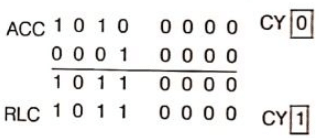

ADD R0, R1: Now, carry flag (CY) = 0

Now, carry flag (CY) = 0

Auxiliary carry (AC) = 0

[∵ No carry fro D3 to D4]

∵ MSB = 1, overflow flag = 1

P = 0 [∵ Four 1's i.e. even number]

∴ Required Flag patter = [CAOP]

= [0010]2 = 2

Q2: An 8085 microprocessor accesses two memory locations (2001 H) and (2002H), that contain 8-bit numbers 98H and B1H respectively. The following program is executed:

LXI H, 2001 H

MVIA, 21H

INX H

ADD M

INX H

MOV M, A

HLT

At the end of this program, the memory location 2003H contains the number in decimal (base 10) form ________ (2020)

(a) 200

(b) 21

(c) 210

(d) 221

Ans: (c)

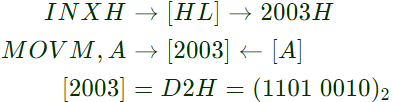

Sol: LXIH, 2001H → [HL] → 2001H

MVIA, 21H → [A] ← 21H

INXH → [HL] → 2002H

ADDM → [A] + [2002] → [A]

= (21H + B1H) → [A]

= D2H → [A] = 1 x 27 + 1 x 26 + 1 x 24 + 1 x 21

= 1 x 27 + 1 x 26 + 1 x 24 + 1 x 21

= 128 + 64 + 16 + 2

= 210

Q3: In 8085A microprocessor, the operation performed by the instruction LHLD 2100H is (SET-3(2014))

(a) (H) ← 21H, (L) ← 00H

(b) (H) ← M(2100H), (L) ← M(2101H)

(c) (H) ← M(2101H), (L) ← M(2100H)

(d) (H) ← 00H, (L) ← 21H

Ans: (c)

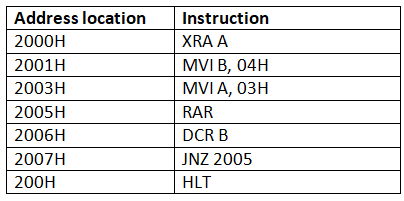

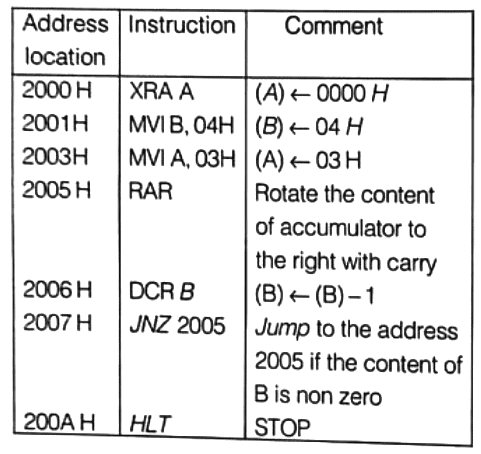

Q4: In an 8085 microprocessor, the following program is executed At the end of program, register A contains (SET-2(2014))

At the end of program, register A contains (SET-2(2014))

(a) 60H

(b) 30H

(c) 06H

(d) 03H

Ans: (a)

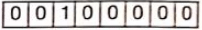

Sol:  For the RAR operation

For the RAR operation and B ← 04

and B ← 04

Similarly for each RAR operation the content of B is decremented by '1' till it becomes 00H. Thus,

B ← 04 A ← 00000011

B ← 03 A ← 10000001

B ← 02 A ← 11000000

B ← 01 A←01100000 B ← 00

Therefore, at the end of the program, egister 'A' contains 60H.

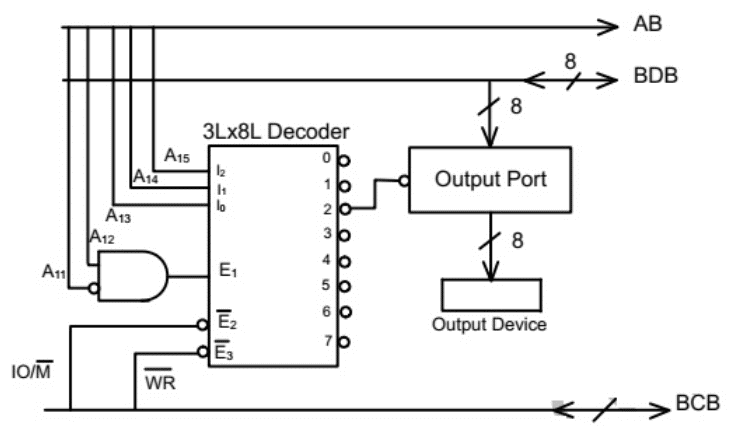

Q5: An output device is interfaced with 8-bit microprocessor 8085A. The interfacing circuit is shown in figure The interfacing circuit makes use of 3 Line to 8 Line decoder having 3 enables lines

The interfacing circuit makes use of 3 Line to 8 Line decoder having 3 enables lines  The address of the device is (SET-1 (2014))

The address of the device is (SET-1 (2014))

(a) 50 H

(b) 5000 H

(c) A0 H

(d) A000 H

Ans: (b)

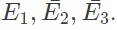

Sol: For the given decoder ∴ A12 should be HIGH and A11 should be LOW.

∴ A12 should be HIGH and A11 should be LOW.

Also, E2 = E3 = 0(disable)

The decoder output depends on I2 = A15, I1 = A14 and I0 = A13 which should be 010 respectively to enable the output port.

The address of the device is 5000H-57FFH,

Q6: A portion of the main program to call a subroutine SUB in an 8085 environment is given below.

:

:

LXI D, DISP

LP : CALL SUB

:

:

It is desired that control be returned to LP + DISP + 3 when the RET instruction is executed in the subroutine. The set of instructions that precede the RET instruction in the subroutine are (2011)

(a)  (b)

(b)  (c)

(c)  (d)

(d)  Ans: (c)

Ans: (c)

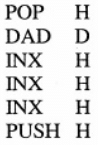

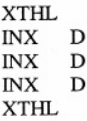

Sol: Call takes 3 address locations, RET always returns to LP+3 location, this stored in SP.

So to return to LP+DISP+3.

We have to add DISP to SP.

POP H

DAD D

PUSH H

Normal call operation shown.

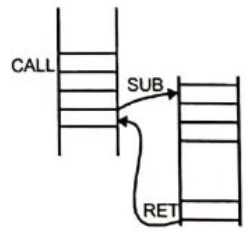

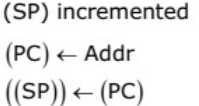

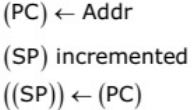

Q7: When a "CALL Addr" instruction is executed, the CPU carries out the following sequential operations internally : (2010)

Note: (R) means content of register R

((R)) means content of memory location pointed to by R.

PC means Program Counter

SP means Stack Pointer

(a)  (b)

(b)  (c)

(c)  (d)

(d)  Ans: (d)

Ans: (d)

Sol: First of all content of PC is loaded into stack i.e. address of next instruction to be executed is loaded onto stack. i.e. SP is decremented then PC is loaded by address given in call instruction.

Q8: In an 8085 microprocessor, the contents of the Accumulator, after the following instructions are executed will become (2009)

XRA A

MVI B, F0 H

SUB B

(a) 01 H

(b) 0F H

(c) F0 H

(d) 10 H

Ans: (d)

Q9: The increasing order of speed of data access for the following device is (2009)

(I) Cache Memory

(II) CD-ROM

(III) Dynamic RAM

(IV) Processor Registers

(V) Magnetic Tape

(a) (V), (II), (III), (IV), (I)

(b) (V), (II), (III), (I), (IV)

(c) (II), (I), (III), (IV), (V)

(d) (V), (II), (I), (III), (IV)

Ans: (b)

Sol: Access time of the residter is very less than that from a memory access. So speed of data access is faster in case of processor register.

Second highest is cache memory because it's size is small, so searching of data takes less time.

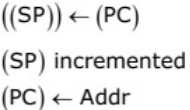

Q10: The content of some of the memory location in an 8085 accumulator based system are given below The content of stack (SP), program counter (PC) and (H, L) are 2700H, 2100H and 0000H respectively. When the following sequence of instruction are executed.

The content of stack (SP), program counter (PC) and (H, L) are 2700H, 2100H and 0000H respectively. When the following sequence of instruction are executed.

2100 H: DAD SP

2101 H: PCHL

the content of (SP) and (PC) at the end of execution will be (2008)

(a) PC = 2102H, SP = 2700H

(b) PC = 2700H, SP = 2700H

(c) PC = 2800H, SP = 26FEH

(d) PC = 2A02H, SP = 2702H

Ans: (b)

Sol: Given,

(SP) = 2700H

(PC) = 2100H

(HL) = 0000H

2100H : DAD SP

(SP) +(HL) → (HL)

2700H + 0000H = 2700H stored in HL pair.

2101H : PCHL : the content of HL are transferred to (PC)

So, now (PC) = 2700H and (SP) also unchanged

(PC) = 2700H

(SP) = 2700H

Q11: An input device is interfaced with Intel 8085A microprocessor as memory mapped I/O. The address of the device is 2500H. In order to input data from the device to accumulator, the sequence of instructions will be (2008)

(a) LXI H, 2500H

MOV A, M

(b) LXI H, 2500H

MOV M, A

(c) LHLD 2500H

MOV A, M

(d) LHLD 2500H

MOV M, A

Ans: (a)

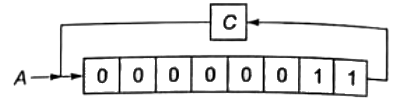

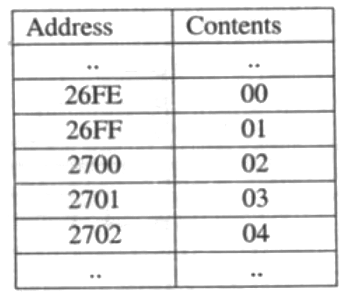

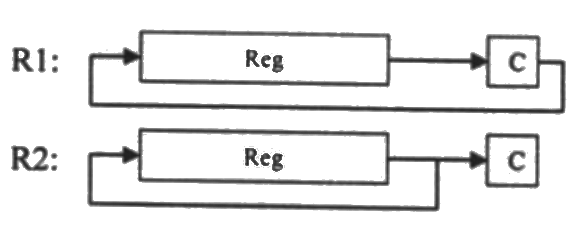

Q12: The associated figure shows the two types of rotate right instructions R1, R2, available in a microprocessor where Reg is a 8-bit register and C is the carry bit. The rotate left instructions L1 and L2 are similar except that C now links the most significant bit of Reg instead of the least significant one. Such a division can be correctly performed by the following set of operatings (2007)

Such a division can be correctly performed by the following set of operatings (2007)

(a) L2, R2, R1

(b) L2, R1, R2

(c) R2, L1, R1

(d) R1, L2, R2

Ans: (a)

Q13: The associated figure shows the two types of rotate right instructions R_1, R_2, available in a microprocessor where Reg is a 8-bit register and C is the carry bit. The rotate left instructions L1 and L2 are similar except that C now links the most significant bit of Reg instead of the least significant one. Suppose Reg contains the 2's complement number 11010110. If this number is divided by 2 the answer should be (2007)

Suppose Reg contains the 2's complement number 11010110. If this number is divided by 2 the answer should be (2007)

(a) 01101011

(b) 10010101

(c) 11101001

(d) 11101011

Ans: (d)

Q14: Which one of the following statements regarding the INT (interrupt) and the BRQ (but request) pins in a CPU is true? (2007)

(a) The BRQ pin is sampled after every instruction cycle, but the INT is sampled after every machine cycle.

(b) Both INT and BRQ are samped after every machine cycle.

(c) The INT pin is sampled after every instruction cycle, but the BRQ is sampled after every machine cycle.

(d) Both INT and BRQ are sampled after every instruction cycle.

Ans: (a)

Q15: In an 8085 A microprocessor based system, it is desired to increment the contents of memory location whose address is available in (D, E) register pair and store the result in same location. The sequence of instruction is (2006)

(a) XCHG

INR M

(b) XCHG

INX H

(c) INX D

XCHG

(d) INR M

XCHG

Ans: (a)

Sol: The address of the memory location is stored in DE register pair. But, INR M command will increase the content of memory location M. but this command will execute only for HL pair. So, we have to exchange the address of memory location in HL pair from DE pair first.

Q16: A software delay subroutine is written as given below :

DELAY : MVI H, 255D

MVI L, 255D

LOOP : DCR L

JNZ LOOP

DCR H

JNZ LOOP

How many times DCR L instruction will be executed ? (2006)

(a) 255

(b) 510

(c) 65025

(d) 62579

Ans: (d)

Sol: First of all DCR L will be executed for 255 times till content of L becomes 0.

After that for every decrement of H it will be executed 256 times ( first when L is decremented by 1 and becomes FFH and then FFH = 255D times ) and this will be happen till content of H become 1 i.e. 254 times.

So, overall it will be executed

= 255 + 254 x 256 = 65279

Q17: The 8085 assembly language instruction that stores the content of H and L register into the memory locations 2050H and 2051H, respectively, is: (2005)

(a) SPHL 2050H

(b) SPHL 2051H

(c) SHLD 2050H

(d) STAX 2051H

Ans: (c)

Sol: Instruction SHLD 2050H stores the content of L to memory location 2050H and content of H to next memory location 2051H.

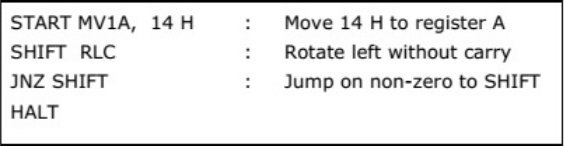

Q18: If the following program is executed in a microprocessor, the number of instruction cycle it will take from START to HALT is (2004) (a) 4

(a) 4

(b) 8

(c) 13

(d) 16

Ans: (d)

Q19: The following program is written for an 8085 microprocessor to add two bytes located at memory addresses 1FFE and 1FFF

LXI H, 1FFE

MOV B, M

INR L

MOV A, M

ADD B

INR L

MOV M, A

XOR A

On completion of the execution of the program, the result of addition is found (2003)

(a) in the register A

(b) at the memory address 1000

(c) at the memory address 1F00

(d) at the memory address 2000

Ans: (c)

Sol: LXI H, 1FFE → Load 1FFE in H-L memory

MOV B, M → move the content of 1FFE memory location to register B

INR L → Increment the content of 'HL' by 1 (1FFE → 1FFF)

MOV A, M → move content of 1FFF memory location to accumulator

ADD B → (A → A + B)

INR L → FF + 1 →00

As result HL → 1F00

MOV M, A → move content of accumulator to memory location 1F00

XRA A → content of accumulator becomes zero

Q20: A memory system has a total of 8 memory chips, each with 12 address lines and 4 data lines, The total size of the memory system is (2003)

(a) 16 kbytes

(b) 32 kbytes

(c) 48 kbytes

(d) 64 kbytes

Ans: (a)

Sol: Total size of memory = No. of chip x data lines

= 4 × 8 × 212

= 128 kbits

= 16 kbyte

Q21: When a program is being executed in an 8085 Microprocessors, its Program Counter contains (2003)

(a) the number of instructions in the current program that have already been executed

(b) the total number of instructions in the program being executed.

(c) the memory address of the instruction that is being currently executed

(d) the memory address of the instruction that is to be executed next

Ans: (d)

Sol: Program counter contains the memory address of the instruction that is to be executed next.

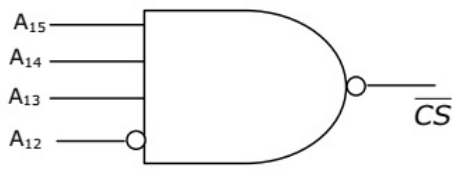

Q22: The logic circuit used to generate the active low chip select (CS) by an 8085 microprocessor to address a peripheral is shown in figure. The peripheral will respond to addresses in the range. (2002) (a) E000-EFFF

(a) E000-EFFF

(b) 000E-FFFE

(c) 1000-FFFF

(d) 0001-FFF1

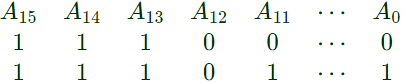

Ans: (a)

Sol:  ⇒ E000 − EFFF

⇒ E000 − EFFF

Q23: An Intel 8085 processor is executing the program given below.

MVI A, 10H

MVI B, 10H

BACK: NOP

ADD B

RLC

JNC BACK

HLT

The number of times that the operation NOP will be executed is equal to (2001)

(a) 1

(b) 2

(c) 3

(d) 4

Ans: (c)

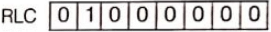

Sol: First loop,

ADD B

Accumulator-20H

Second loop:

Second loop: Third loop:

Third loop: Carry is generated. Now program will hault. So NOP instruction is executed 3 times.

Carry is generated. Now program will hault. So NOP instruction is executed 3 times.

|

213 videos|208 docs|72 tests

|

FAQs on Previous Year Questions- Microprocessors - Analog and Digital Electronics - Electrical Engineering (EE)

| 1. What are the basic functions of a microprocessor in electrical engineering? |  |

| 2. How does the architecture of a microprocessor affect its performance? |  |

| 3. What are some common applications of microprocessors in electrical engineering? |  |

| 4. What are the key differences between a microprocessor and a microcontroller? |  |

| 5. What are the popular microprocessor families used in electrical engineering? |  |