Computer Science Engineering (CSE) Exam > Computer Science Engineering (CSE) Notes > Embedded Systems (Web) > Cheatsheet: Embedded Systems (Web)

Cheatsheet: Embedded Systems (Web)

1. Fundamentals of Embedded Systems

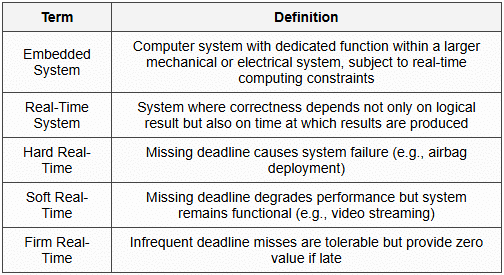

1.1 Core Definitions

1.2 Characteristics

- Application-specific requirements and dedicated functionality

- Real-time operation with timing constraints

- Low power consumption requirements

- Reactive to external environment via sensors/actuators

- High reliability and safety requirements

- Resource constraints (memory, processing power)

- Cost-sensitive design

1.3 Classifications

2. Microprocessors and Microcontrollers

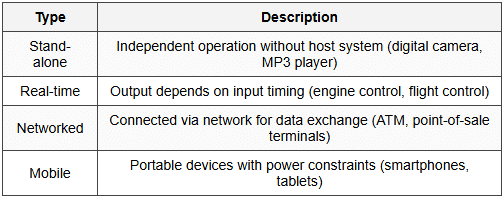

2.1 Comparison

2.2 Processor Architectures

2.2.1 Von Neumann Architecture

- Single memory space for instructions and data

- Single bus for data and instructions (Von Neumann bottleneck)

- Simpler hardware design

- Sequential instruction fetch and data access

2.2.2 Harvard Architecture

- Separate memory spaces for instructions and data

- Separate buses enable simultaneous access

- Higher performance and throughput

- Used in many embedded processors, typically in modified Harvard architecture form

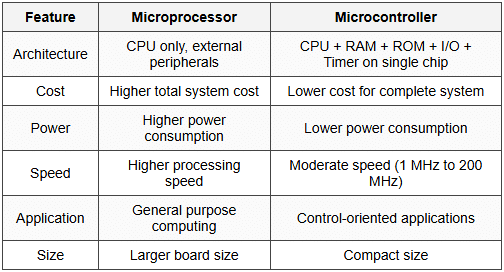

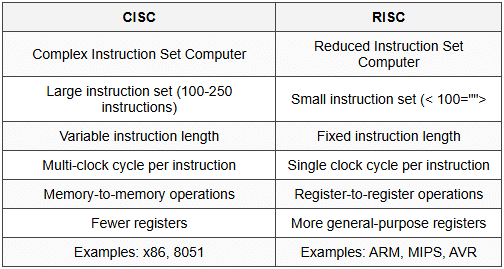

2.3 Instruction Set Architectures

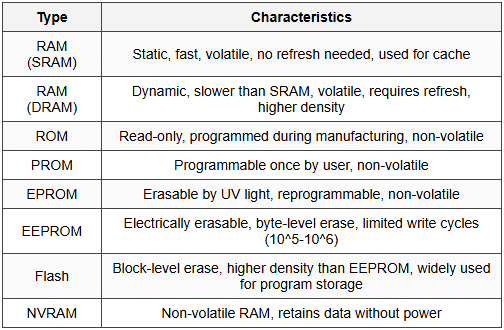

3. Memory Systems

3.1 Memory Types

3.2 Memory Hierarchy

- Level 0: CPU Registers (fastest, smallest)

- Level 1: Cache Memory (L1 - on chip, split I-cache and D-cache)

- Level 2: Cache Memory (L2 - larger, may be on-chip or off-chip)

- Level 3: Main Memory (RAM - DRAM)

- Level 4: Secondary Storage (Flash, HDD - slowest, largest)

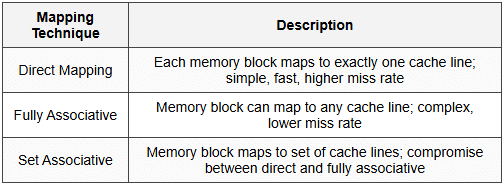

3.3 Cache Memory

3.4 Cache Performance Metrics

- Hit Rate = (Cache Hits) / (Total Accesses)

- Miss Rate = 1 - Hit Rate = (Cache Misses) / (Total Accesses)

- Average Access Time (single-level cache) = Hit Time + (Miss Rate × Miss Penalty)

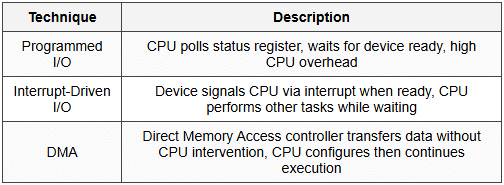

4. Input/Output Systems

4.1 I/O Interfacing Techniques

4.2 Interrupts

4.2.1 Types

- Maskable Interrupts: Can be enabled/disabled by software

- Non-Maskable Interrupts (NMI): Cannot be disabled, highest priority

- Vectored Interrupts: Each interrupt has fixed vector address

- Non-Vectored Interrupts: Single interrupt vector, polling required to identify source

4.2.2 Interrupt Handling Steps

- Complete current instruction execution

- Save program counter and processor status

- Identify interrupt source (implicit via vector or explicit via polling)

- Jump to Interrupt Service Routine (ISR)

- Execute ISR

- Restore saved context

- Return to interrupted program

4.3 DMA Operation

- CPU programs DMA controller with source, destination, byte count

- DMA requests bus control from CPU

- CPU grants bus (enters hold/tri-state)

- DMA transfers data directly between memory and peripheral

- DMA releases bus and interrupts CPU when complete

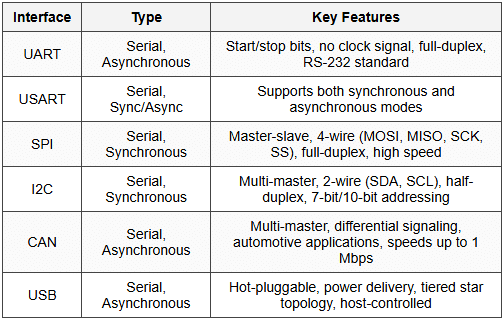

4.4 Communication Interfaces

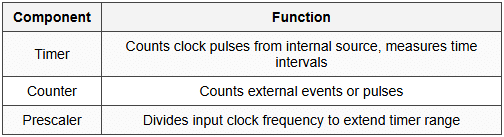

5. Timers and Counters

5.1 Definitions

5.2 Timer Modes

- Free Running Mode: Counts continuously, wraps around at maximum

- One-Shot Mode: Counts once, stops at terminal count

- PWM Mode: Generates pulse width modulated output

- Capture Mode: Records timer value when external event occurs

- Compare Mode: Generates output when timer matches compare value

5.3 Watchdog Timer

- Safety mechanism to recover from software malfunctions

- Must be periodically reset by software

- Generates system reset if not serviced within timeout period

- Prevents system hang or infinite loops

6. Analog Interfacing

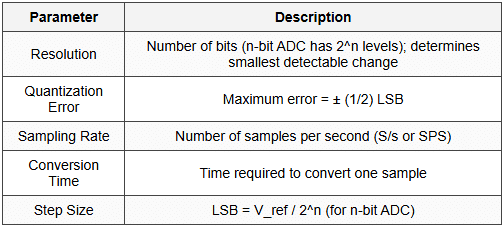

6.1 ADC (Analog-to-Digital Converter)

6.1.1 Key Parameters

6.1.2 Sampling Theorem

- Nyquist-Shannon Theorem: f_sample ≥ 2 × f_max

- Sampling frequency must be at least twice the maximum signal frequency to avoid aliasing

- Anti-aliasing filters remove high-frequency components before sampling

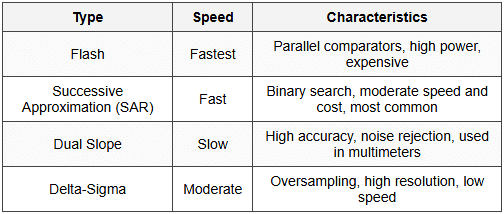

6.1.3 ADC Types

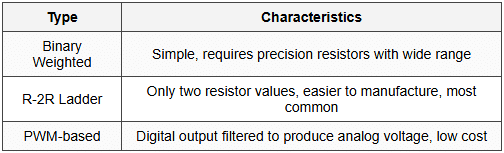

6.2 DAC (Digital-to-Analog Converter)

6.2.1 Key Parameters

- Resolution: n bits determines 2^n output levels

- Settling Time: Time to reach final value within specified error

- Step Size: V_out_step = V_ref / 2^n

6.2.2 DAC Types

7. Power Management

7.1 Power Consumption Components

- Dynamic Power: P_dynamic = α × C × V_dd² × f (switching activity)

- Static Power: P_static = I_leakage × V_dd (leakage current)

- Short-Circuit Power: During switching transitions

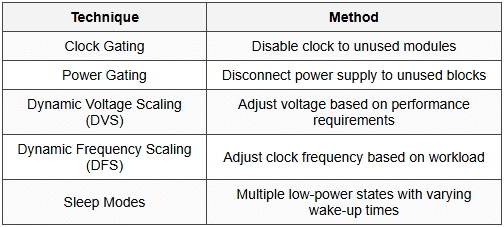

7.2 Power Reduction Techniques

7.3 Processor Sleep Modes

- Idle Mode: CPU stopped, peripherals active, fastest wake-up

- Sleep Mode: CPU and some peripherals stopped, RAM retained

- Deep Sleep: Most peripherals off, only RTC and wake-up sources active

- Standby/Shutdown: Minimum power, longest wake-up time, limited state retention

8. Real-Time Operating Systems (RTOS)

8.1 RTOS Characteristics

- Deterministic behavior with bounded response times

- Preemptive multitasking with priority-based scheduling

- Minimal interrupt latency and context switch overhead

- Small memory footprint

- Support for inter-task communication and synchronization

8.2 Task States

- Ready: Ready to execute, waiting for CPU

- Running: Currently executing on CPU

- Blocked/Waiting: Waiting for event or resource

- Suspended: Explicitly suspended, not scheduled

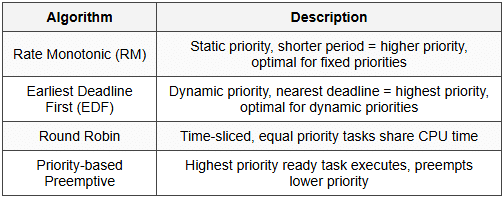

8.3 Scheduling Algorithms

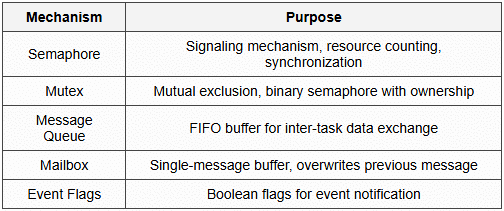

8.4 Inter-Task Communication

8.5 Priority Inversion Problem

- High-priority task blocked by low-priority task holding shared resource

- Medium-priority task preempts low-priority task, delaying high-priority task

- Solution 1: Priority Inheritance (low-priority task inherits high-priority temporarily)

- Solution 2: Priority Ceiling (task accessing resource gets highest priority of all tasks that use it)

8.6 Schedulability Analysis

- Rate Monotonic: CPU utilization ≤ n(2^(1/n) - 1) for n tasks

- For n → ∞, utilization bound ≈ 69.3%

- EDF: CPU utilization ≤ 100% (theoretical)

- Response Time: R_i = C_i + Σ(⌈R_i/T_j⌉ × C_j) for higher priority tasks j

9. Design Metrics and Optimization

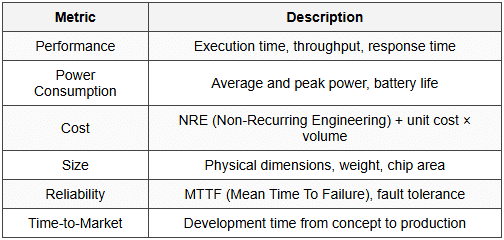

9.1 Key Design Metrics

9.2 Hardware-Software Co-Design

- Concurrent design of hardware and software components

- Partitioning: Decide which functions implemented in hardware vs software

- Hardware: Faster, parallel, higher cost, less flexible

- Software: Slower, sequential, lower cost, more flexible

- Trade-offs: Performance vs cost, flexibility vs speed

9.3 Design Flow

- Requirements Specification: Functional and non-functional requirements

- Architecture Design: Select processor, memory, peripherals

- Hardware/Software Partitioning: Allocate functions

- Component Design: Detailed hardware and software design

- System Integration: Combine hardware and software

- Verification and Validation: Testing, debugging

- Manufacturing and Deployment

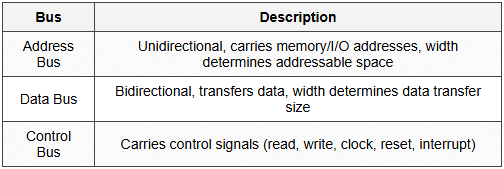

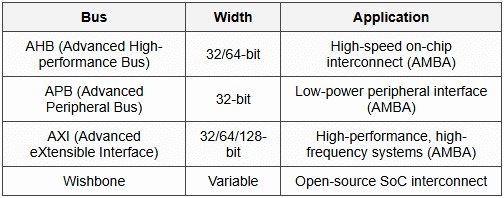

10. Bus Systems and Protocols

10.1 Bus Types

10.2 Bus Arbitration

- Centralized: Single bus controller grants access (simple, single point of failure)

- Distributed: Devices negotiate bus access (more complex, no single point of failure)

- Daisy Chain: Priority determined by position in chain

- Polling: Controller polls devices in sequence

- Independent Request: Each device has request and grant lines

10.3 Common Bus Standards

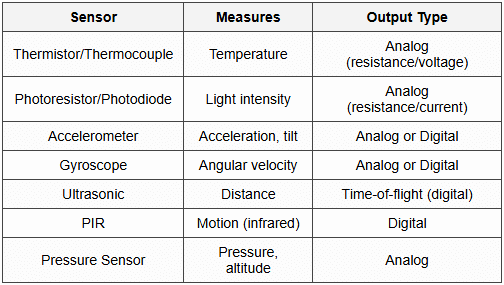

11. Sensors and Actuators

11.1 Common Sensors

11.2 Signal Conditioning

- Amplification: Increase signal amplitude to match ADC range

- Filtering: Remove noise (low-pass, high-pass, band-pass)

- Isolation: Protect processor from high voltage/current

- Linearization: Convert non-linear sensor output to linear

- Level Shifting: Adjust DC offset to ADC input range

11.3 Common Actuators

- DC Motor: Continuous rotation, speed control via PWM

- Stepper Motor: Precise angular positioning, step-by-step rotation

- Servo Motor: Closed-loop position control, limited rotation range

- Relay: Electromechanical switch for high-power loads

- Solenoid: Linear actuator, electromagnetic coil

- LED/LCD: Visual output display

- Speaker/Buzzer: Audio output

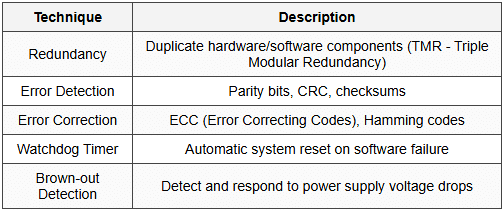

12. Design Considerations

12.1 Reliability and Fault Tolerance

12.2 Security Considerations

- Secure Boot: Verify firmware integrity before execution

- Encryption: Protect data in storage and transmission (AES, RSA)

- Authentication: Verify user/device identity

- Access Control: Restrict access to resources and memory regions

- Side-Channel Attack Protection: Prevent timing, power analysis attacks

12.3 Testing and Debugging

- JTAG: IEEE 1149.1 standard for boundary scan testing and debugging

- In-Circuit Emulator (ICE): Hardware tool for real-time debugging

- Logic Analyzer: Capture and analyze digital signals

- Oscilloscope: Measure and visualize analog signals

- Unit Testing: Test individual software modules

- Integration Testing: Test combined hardware-software system

- Boundary Scan: Test interconnections between chips

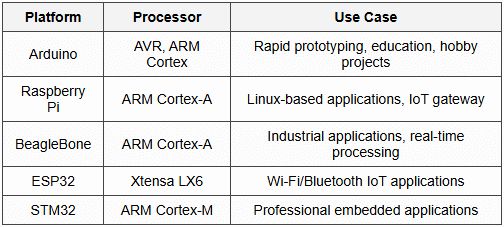

12.4 Common Embedded Platforms

13. Performance Analysis

13.1 Timing Analysis

- Execution Time: Time to complete task or instruction

- Response Time: Time from input to output

- Latency: Delay in processing or communication

- Throughput: Amount of work completed per unit time

- WCET (Worst Case Execution Time): Maximum execution time for task

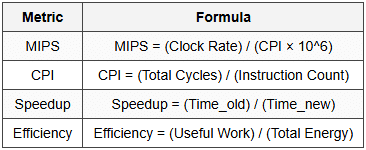

13.2 Performance Metrics

13.3 Memory Performance

- Memory Bandwidth: Data transfer rate (bytes/second)

- Access Time: Time to read/write data

- Cycle Time: Minimum time between successive accesses

- Effective Access Time = (Hit Rate × Cache Time) + (Miss Rate × Memory Time)

The document Cheatsheet: Embedded Systems (Web) is a part of the Computer Science Engineering (CSE) Course Embedded Systems (Web).

All you need of Computer Science Engineering (CSE) at this link: Computer Science Engineering (CSE)

FAQs on Cheatsheet: Embedded Systems (Web)

| 1. What are the key components of an embedded system? |  |

Ans. An embedded system typically consists of a microprocessor or microcontroller, memory, input/output systems, and peripherals. These components work together to perform specific tasks within a larger system, such as controlling machinery or processing data.

| 2. How do microprocessors differ from microcontrollers? |  |

Ans. Microprocessors are designed to perform a variety of tasks and are typically used in computers, whereas microcontrollers integrate a processor, memory, and input/output peripherals on a single chip, making them ideal for specific control-oriented applications in embedded systems.

| 3. What role do timers and counters play in embedded systems? |  |

Ans. Timers and counters are crucial for time management and event counting in embedded systems. Timers can generate precise time delays or intervals for executing tasks, while counters can keep track of occurrences, such as measuring frequency or counting pulses from an input signal.

| 4. Why is power management important in embedded systems? |  |

Ans. Power management is essential in embedded systems to ensure efficient operation, especially in battery-powered devices. Effective power management techniques help prolong battery life, reduce heat generation, and improve overall system performance by optimising power consumption during various operational states.

| 5. What is the significance of real-time operating systems (RTOS) in embedded applications? |  |

Ans. Real-time operating systems (RTOS) are designed to manage resources and tasks in a way that guarantees timely execution. This is critical in embedded applications where timing is crucial, such as in automotive systems or medical devices, where delays could lead to system failure or safety issues.

| Explore Courses for Computer Science Engineering (CSE) exam |  |

| Get EduRev Notes directly in your Google search |  |

Related Searches

practice quizzes, video lectures, study material, Summary, past year papers, Extra Questions, Exam, Semester Notes, Sample Paper, Free, MCQs, ppt, shortcuts and tricks, Objective type Questions, Viva Questions, pdf , mock tests for examination, Cheatsheet: Embedded Systems (Web), Previous Year Questions with Solutions, Cheatsheet: Embedded Systems (Web), Important questions, Cheatsheet: Embedded Systems (Web);