GATE Computer Science Engineering(CSE) 2027 Test: Secondary Memory & DMA-

MCQ Practice Test & Solutions: Test: Secondary Memory & DMA- 2 (8 Questions)

You can prepare effectively for Computer Science Engineering (CSE) GATE Computer Science Engineering(CSE) 2027 Mock Test Series with this dedicated MCQ Practice Test (available with solutions) on the important topic of "Test: Secondary Memory & DMA- 2". These 8 questions have been designed by the experts with the latest curriculum of Computer Science Engineering (CSE) 2026, to help you master the concept.

Test Highlights:

- - Format: Multiple Choice Questions (MCQ)

- - Duration: 25 minutes

- - Number of Questions: 8

Sign up on EduRev for free to attempt this test and track your preparation progress.

Detailed Solution: Question 1

Compare the following by considering data transfer rate:

1. I/O processor

2. Data communication processor

1. I/O processor

2. Data communication processor

Detailed Solution: Question 2

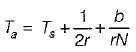

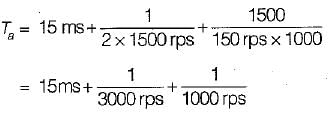

Consider a Disk I/O transfer, in which 1500 bytes are to be transferred, but number of bytes on a track is 1000, and rotation speed of disk is 1500 rps but the average time required to move the disk arm to the required track is 15 ms, then what will be total access time?

Detailed Solution: Question 3

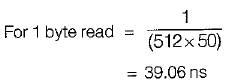

The computer can execute 1,000,000 instructions per second: A program running on this computer performs on average a one sector read and one sector write for every 200 instructions that it executes. The disk drive handling the I/O transfers requires 0.00010 seconds each to perform the read and write operations. Assuming no overlap of these operations, the percent of CPU time spent in the wait state is

Detailed Solution: Question 4

In a general purpose computer system the CPU, the main memory and the cache may be interconnected via one or more shared system bus(es). However, input/output devices (eg. Hard disk, network interfaces) may only be connected to the system bus through an I/O controller. The following are four statements regarding the requirement for an I/O controller.

1. The capacities of I/O devices are magnitude order larger than that of main memory and hence direct interfacing is impossible.

2. The response times of I/O devices are magnitude order slower than that of CPU and hence direct interfacing is impossible.

3. It is always better to off load the I/O processing to a secondary processor on the I/O controller board then to depend on the primary CPU for I/O processing.

4. The variety of I/O devices in the market requires that a separate I/O controller exist for each device.

Q. What statement(s) best explain the requirement for an I/O controller?

1. The capacities of I/O devices are magnitude order larger than that of main memory and hence direct interfacing is impossible.

2. The response times of I/O devices are magnitude order slower than that of CPU and hence direct interfacing is impossible.

3. It is always better to off load the I/O processing to a secondary processor on the I/O controller board then to depend on the primary CPU for I/O processing.

4. The variety of I/O devices in the market requires that a separate I/O controller exist for each device.

An 8-Bit DMA Device is operating is Cycle Stealing Mode (Single Transfer Mode). Each DMA cycle is of 6 clock states and DMA clock is 2 MHz. Intermediate CPU machine cycle takes 2 μs, determine the DMA Data Transfer Rate

Detailed Solution: Question 6

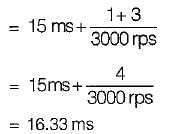

A device with data transfer rate 10 KB/sec is connected to a CPU. Data is transferred byte- wise. Let the interrupt overhead be 4 μsec. The byte transfer time between the device interface register and CPU or memory is negligible. What is the minimum performance gain of operating the device under interrupt mode over operating it under program controlled mode?

Detailed Solution: Question 7

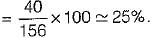

Consider a disk drive with the following specifications: 16 surfaces, 512 tracks / surface, 512 sectors / track, 1 KB/sector, rotation speed 3000 rpm. The disk is operated in cycle stealing mode whereby whenever one byte word is ready it is sent to memory; similarly, for writing, the disk interface reads a 4 byte word from the memory in each DMA cycle. Memory cycle time is 40 nsec. The maximum percentage of time that the CPU gets blocked during DMA operation is

Detailed Solution: Question 8