GATE ECE (Electronics) Test: Digital Electronics- 3 Free Online Test 2026

MCQ Practice Test & Solutions: Test: Digital Electronics- 3 (25 Questions)

You can prepare effectively for Electronics and Communication Engineering (ECE) GATE ECE (Electronics) Mock Test Series 2027 with this dedicated MCQ Practice Test (available with solutions) on the important topic of "Test: Digital Electronics- 3". These 25 questions have been designed by the experts with the latest curriculum of Electronics and Communication Engineering (ECE) 2026, to help you master the concept.

Test Highlights:

- - Format: Multiple Choice Questions (MCQ)

- - Duration: 75 minutes

- - Number of Questions: 25

Sign up on EduRev for free to attempt this test and track your preparation progress.

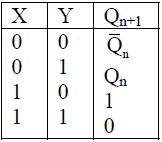

An X-Y flip flop whose characteristic table is given below is to be implemented using a T flip flop

This can be done by making

Which of the following ADC has a fixed conversion time?

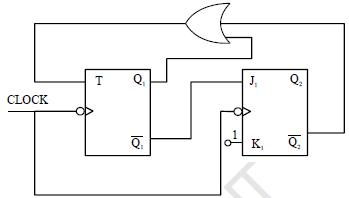

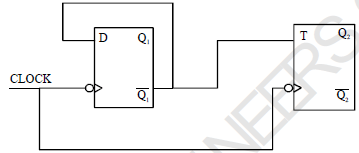

The sequence (Q2 Q1) when successive clock pulses are applied

A number P represented in signed binary 2’s complement form is 1001101. Another number Q1 represented in signed binary 2’s complement form is 11010111. If Q is subtracted from P, the result expressed in signed binary 2’s complement form

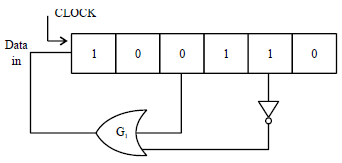

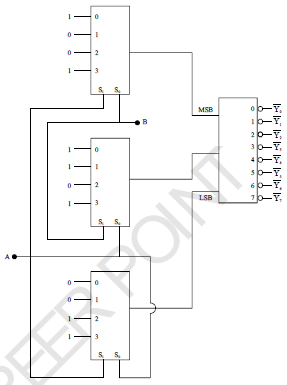

Figure shows the initial content of a 6 bit SIPO register with each clock pulse output of gate G1 is pushed in the left most stage. What will be the content of the register after 9th clock pulse?

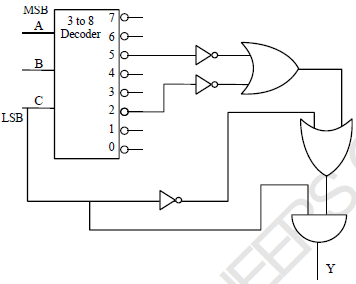

The function y (A, B, C) implemented by the circuit shown is

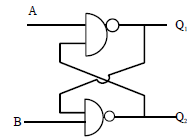

In the latch circuit shown if A = 1, B = 0 is applied, the corresponding stable outputs are

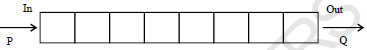

A digital bit is to be transmitted from point P to point Q by delaying it through a SISO register of 8 bit as shown. If the clock frequency used is 4 MHz, the delay created by the register is

Detailed Solution: Question 11

The resistance corresponding to LSB in a weighted resistor 5 bit DAC i s 64 k?, then the resistor corresponding to MSB is

The output of a 6bit DAC for the digital input of 1001000 is 300 volts. What will be the DAC output for digital input 1101010 approximately

In the circuit shown in figure, to make  Low, what must be conditions at A and B

Low, what must be conditions at A and B

The counting sequence (Q1 Q2) when clock pulses are applied

The binary equivalent of the gray code (1011100 11)G

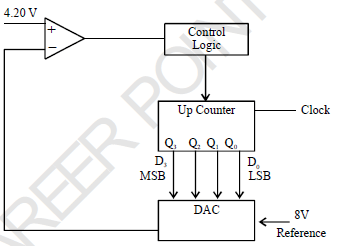

An analog input of 4.20 Volt is to be converted into digital form using counter type ADC. The digital equivalent will be [Taking threshold voltage of comparator as one tenth of DAC resolution)

The present state of a JK flip flop was 0. After one clock pulse, it was found to be 0. What possible inputs

may be applied?

may be applied?

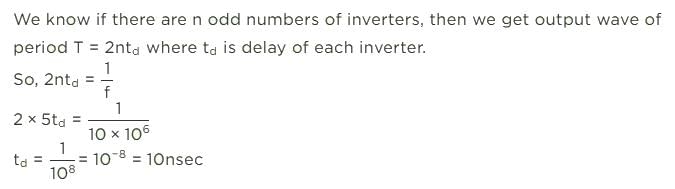

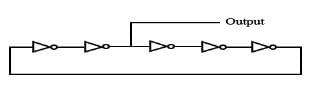

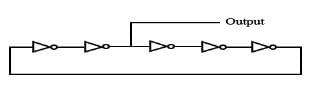

The inverters in the ring oscillator circuit shown below are identical. If the output waveform has a frequency of 10 MHz, the propagation delay of each inverter is

Detailed Solution: Question 24

26 docs|263 tests |