Test: Logic Families - 2 - Electrical Engineering (EE) MCQ

15 Questions MCQ Test - Test: Logic Families - 2

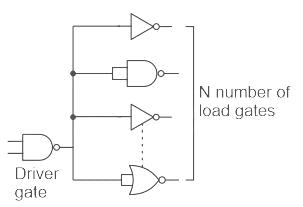

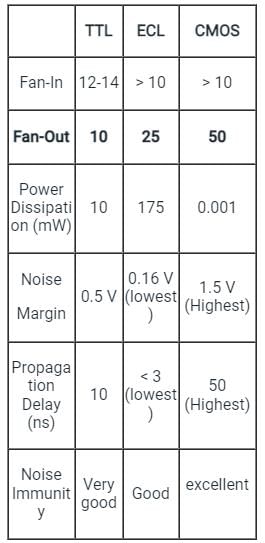

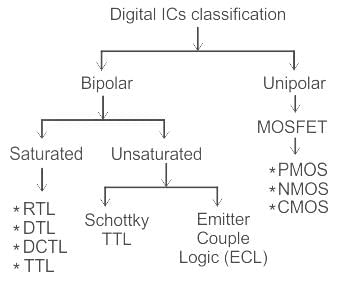

Which of the following IC logic families has minimum value of fan-out?

Which of the following IC logic families has the highest fan-out?

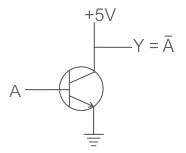

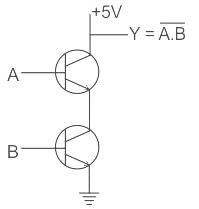

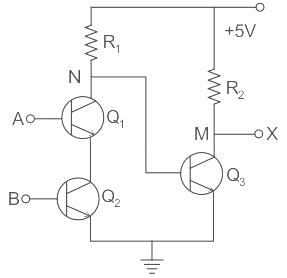

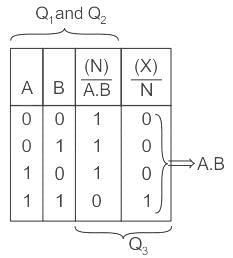

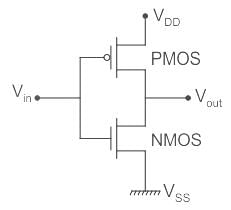

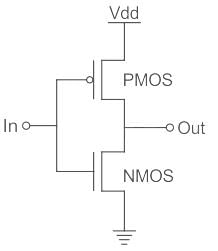

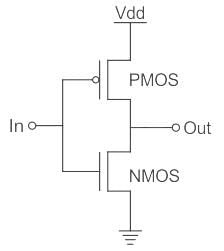

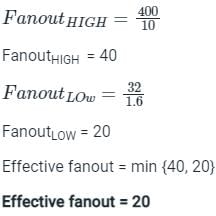

If A and B are the logical inputs to the following circuit, determine the logical relation between the inputs and the output X.

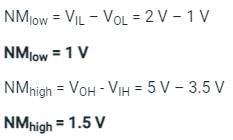

A particular logic family has VOH = 5 V, VOL = 1 V, VIH = 3.5 V and VIL = 2 V. The noise margin values NMH and NML will be

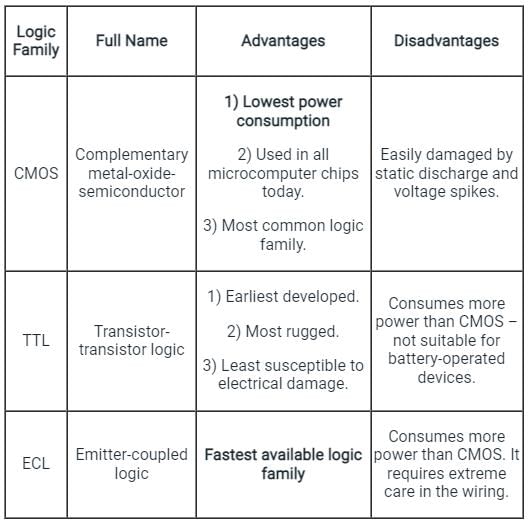

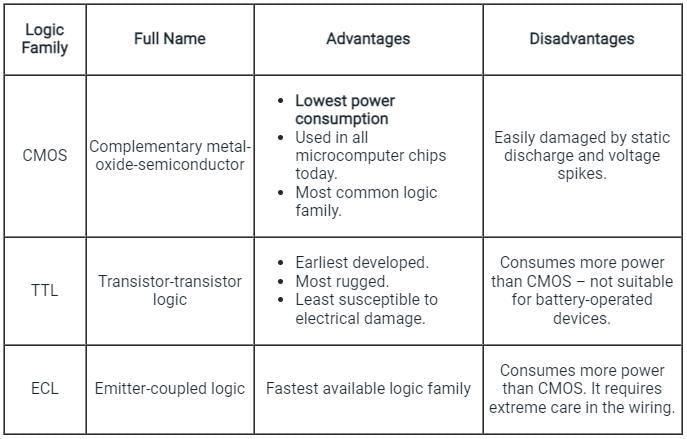

Which among the following is the fastest switching logic family?

Which of the following logic families requires maximum power?

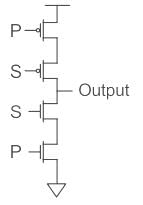

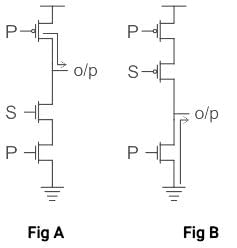

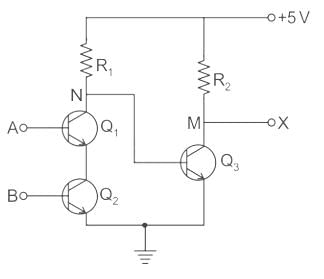

Output of the circuit shown below when S = 1 and S = 0 will be _____.

For a typical CMOS process, the minimum feature size is set to be 25 μm. The minimum line width at the process is set to be ______

Which of the following logic gates can be used to implement the functionality of any logic gate?

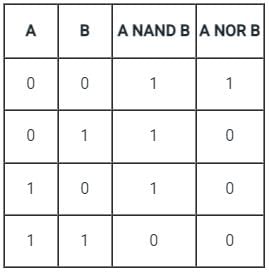

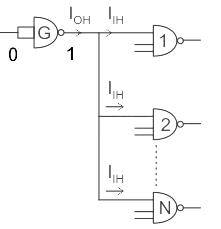

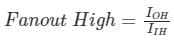

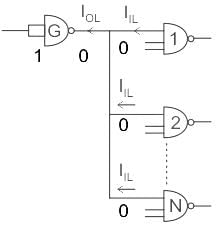

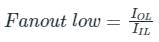

Calculate the fan out of a TTL circuit with the following specifications:

IOL(max) = 32 mA, IIL(max) = 1.6 mA, IOH(max) = 400 uA, IIH(max) = 10 uA

and similarly,

and similarly,