Test: Binary Adders - GATE MCQ

10 Questions MCQ Test - Test: Binary Adders

In which of the following adder circuits, the carry look ripple delay is eliminated?

For an n-bit binary adder, what is the number of gates through which a carry has to propagate from input to output?

| 1 Crore+ students have signed up on EduRev. Have you? Download the App |

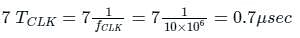

A serial adder is operating with a clock frequency of 10 MHz. Time required to sum 1010111 and 10111 number is –(in μsec)

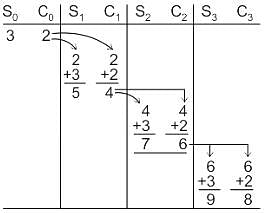

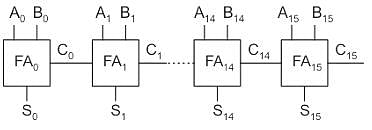

A 16-bit ripple carry adder is realized using 16 identical full adders (FA) as shown in the figure. The carry-propagation delay of each FA is 12 ns and the sum-propagation delay of each FA is 15 ns. The worst case delay (in ns) of this 16-bit adder will be __________.

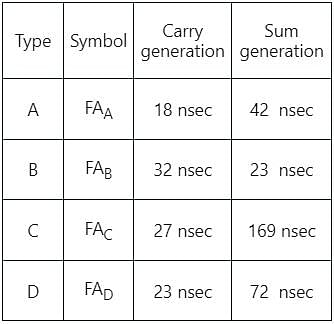

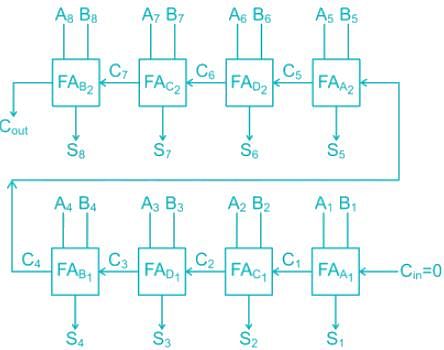

Four different types of Adders are used to construct an 8-bit adder. The characteristic of each full adder in terms of delay is as follows:

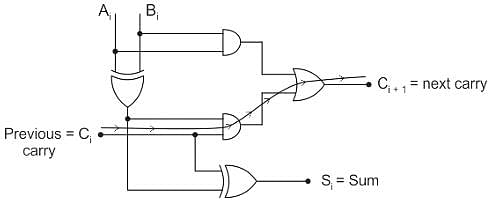

The structure of the FA is as follows:

The maximum no of addition per second that the above adder can perform is –

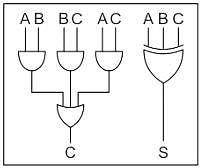

Consider a 4 bit ripple carry adder. Each full adder is implemented using a 3 input exor gate, three 2 input AND gates and one 3 input or gate. Consider the delay of 3 input exor gate to be 3 n-sec, the delay of each 2 input AND gate to be 1 nsec and the delay of each 3 input or gate to be 1 nsec. The total time taken by the 4 bit ripple carry adder to perform successful addition operation is ________.

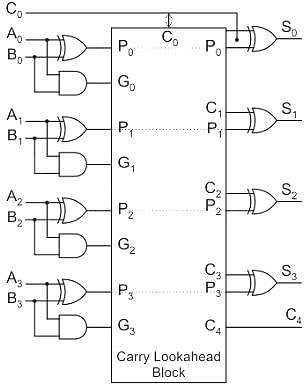

Let x be the number of AND gates present in the 4 bit carry look ahead adder and y be the number of OR gates presents in that adder then the value of 2x + 2y is ____________

The number of logic gates and the way of their interconnections can be classified as ____________

The output sum of two decimal digits can be represented in ____________