Computer Science Engineering (CSE) Exam > Computer Science Engineering (CSE) Tests > Test: Combinational Circuits - Computer Science Engineering (CSE) MCQ

Test: Combinational Circuits - Computer Science Engineering (CSE) MCQ

Test Description

10 Questions MCQ Test - Test: Combinational Circuits

Test: Combinational Circuits for Computer Science Engineering (CSE) 2024 is part of Computer Science Engineering (CSE) preparation. The Test: Combinational Circuits questions and answers have been prepared

according to the Computer Science Engineering (CSE) exam syllabus.The Test: Combinational Circuits MCQs are made for Computer Science Engineering (CSE) 2024 Exam.

Find important definitions, questions, notes, meanings, examples, exercises, MCQs and online tests for Test: Combinational Circuits below.

Solutions of Test: Combinational Circuits questions in English are available as part of our course for Computer Science Engineering (CSE) & Test: Combinational Circuits solutions in

Hindi for Computer Science Engineering (CSE) course.

Download more important topics, notes, lectures and mock test series for Computer Science Engineering (CSE) Exam by signing up for free. Attempt Test: Combinational Circuits | 10 questions in 30 minutes | Mock test for Computer Science Engineering (CSE) preparation | Free important questions MCQ to study for Computer Science Engineering (CSE) Exam | Download free PDF with solutions

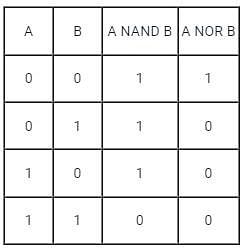

Detailed Solution for Test: Combinational Circuits - Question 1

Test: Combinational Circuits - Question 2

Number of 2 × 1 Multiplexers are required to implement 64 × 1 Multiplexers

Detailed Solution for Test: Combinational Circuits - Question 2

| 1 Crore+ students have signed up on EduRev. Have you? Download the App |

Detailed Solution for Test: Combinational Circuits - Question 3

Detailed Solution for Test: Combinational Circuits - Question 4

Test: Combinational Circuits - Question 5

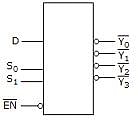

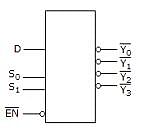

For the device shown here, assume the D input is LOW, both S inputs are LOW and the input is LOW. What is the status of the Y’ outputs?

Detailed Solution for Test: Combinational Circuits - Question 5

Test: Combinational Circuits - Question 6

What is the indication of a short to ground in the output of a driving gate?

Detailed Solution for Test: Combinational Circuits - Question 6

Test: Combinational Circuits - Question 7

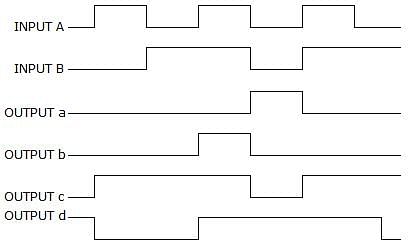

For a two-input XNOR gate, with the input waveforms as shown below, which output waveform is correct?

Detailed Solution for Test: Combinational Circuits - Question 7

Detailed Solution for Test: Combinational Circuits - Question 8

Detailed Solution for Test: Combinational Circuits - Question 9

Test: Combinational Circuits - Question 10

Which of the following combinations of logic gates can decode binary 1101?

Detailed Solution for Test: Combinational Circuits - Question 10

Information about Test: Combinational Circuits Page

In this test you can find the Exam questions for Test: Combinational Circuits solved & explained in the simplest way possible.

Besides giving Questions and answers for Test: Combinational Circuits, EduRev gives you an ample number of Online tests for practice

Download as PDF