Test: Instructions & Input Output Interface - Computer Science Engineering (CSE) MCQ

15 Questions MCQ Test - Test: Instructions & Input Output Interface

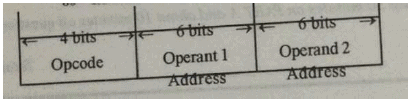

Using an expanding opcode encoding for instructions, is it possible to encode all of the following in an instruction format

shown in the below figure. Justify your answer.

14 double address instructions

127 single address instructions

60 no address (zero address) instructions

shown in the below figure. Justify your answer.

14 double address instructions

127 single address instructions

60 no address (zero address) instructions

Which of the following statements is true?

Which of the following is not a form of memory

Consider a new instruction named branch-on-bit-set (mnemonic bbs). The instruction “bbs reg, pos, label” jumps to label if bit in position pos of register operand reg is one. A register is 32 bits wide and the bits are numbered 0 to 31, bit in position 0 being the least significant. Consider the following emulation of this instruction on a processor that does not have bbs implemented.

Branch to label if temp is non-zero. The variable temp is a temporary register. For correct emulation, the variable mask must be generated by

Consider a RISC machine where each instruction is exactly 4 bytes long. Conditional and unconditional branch instructions use PC-relative addressing mode with Offset specified in bytes to the target location of the branch instruction. Further the Offset is always with respect to the address of the next instruction in the program sequence. Consider the following

instruction sequence Instr. No. Instruction

i : add R2, R3, R4

i + 1 : sub R5, R6, R7

i + 2 : cmp R1, R9, R10

i + 3 : beq R1, Offset

If the target of the branch instruction is i, then the decimal value of the Offset is ____________

Consider a processor with 64 registers and an instruction set of size twelve. Each instruction has five distinct fields, namely, opcode, two source register identifiers, one destination register identifier, and twelve-bit immediate value. Each instruction must be stored in memory in a byte-aligned fashion. If a program has 100 instructions, the amount of memory (in bytes)

consumed by the program text is _________.

In an 11-bit computer instruction format, the size of address field is 4-bits. The computer uses expanding OP code technique and has 5 two-address instructions and 32 one-address instructions. The number of zero-address instructions it can support is ________

State True or False with one line explanation Expanding opcode instruction formats are commonly employed in RISC. (Reduced Instruction Set Computers) machines.

A machine has a 32-bit architecture, with 1-word long instructions. It has 64 registers, each of which is 32 bits long. It needs to support 45 instructions, which have an immediate operand in addition to two register operands. Assuming that the immediate operand is an unsigned integer, the maximum value of the immediate operand is ____________

Many of the advanced microprocessors prefetch instructions and store it in an instruction buffer to speed up processing. This speed up is achieved because ________

On receiving an interrupt from a I/O device the CPU:

A device employing INTR line for device interrupt puts the CALL instruction on the data bus while

A device with data transfer rate 10 KB/sec is connected to a CPU. Data is transferred byte-wise. Let the interrupt overheadbe 4 sec. The byte transfer time between the device interface register and CPU or memory is negligible. What is theminimum performance gain of operating the device under interrupt mode over operating it under program-controlled mode?