Test: Digital Electronics - 3 - Electrical Engineering (EE) MCQ

25 Questions MCQ Test - Test: Digital Electronics - 3

The range of signed decimal number that can be represented by 6 bit in complement number is

| 1 Crore+ students have signed up on EduRev. Have you? Download the App |

In 8085 microprocessor, which of the following interrupts has the highest priority?

Assertion (A): An SR latch has the problem of RAC condition

Reason (R): While designing a digital circuit RAC condition should be avoided.

In 1-to-4 demultiplexer, how many select lines are required?

In Von-Neumann-or Princeton-type computers, the program

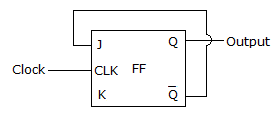

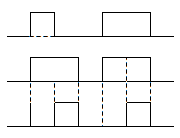

For the circuit shown in the figure, what is the frequency of the output Q?

How many input-output ports can be accessed by direct method of 8085 μp?

When two 16-input multiplexers drive a 2-input MUX, what is the result?

In floating point number 0110100000010101, the exponent is equal to __________ 10

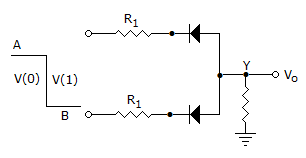

figure shows three pulse train inputs to a 3-input OR gate. Assuming positive logic, the output pulse rate train in figure (b) would be

The advantage of using dual slope ADC in digital voltmeter is that

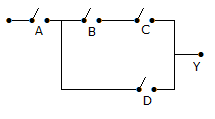

For the switch circuit, taking open as 0 and closed as 1, the expression for the circuit is Y. Y is given by

Assuming accumulator contain A 64 and the carry is set (1).What will register A and (CY) contain after RAR?