GATE Electrical Engineering (EE) Test: Decoders Free Online Test 2026

MCQ Practice Test & Solutions: Test: Decoders (15 Questions)

You can prepare effectively for Electrical Engineering (EE) GATE Electrical Engineering (EE) Mock Test Series 2027 with this dedicated MCQ Practice Test (available with solutions) on the important topic of "Test: Decoders". These 15 questions have been designed by the experts with the latest curriculum of Electrical Engineering (EE) 2026, to help you master the concept.

Test Highlights:

- - Format: Multiple Choice Questions (MCQ)

- - Duration: 30 minutes

- - Number of Questions: 15

Sign up on EduRev for free to attempt this test and track your preparation progress.

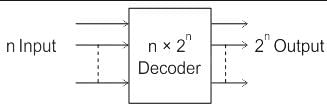

How many 3 × 8 decoders are required to Construct a 4 × 16 decoder?

Detailed Solution: Question 1

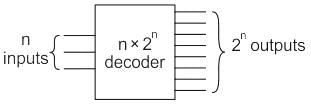

A _________ is a multiple-input, multiple-output logic circuit which converts coded inputs into coded outputs, where the input and output code are different.

Detailed Solution: Question 2

___________ converts binary-coded information to unique outputs such as decimal, octal digits, etc.

Detailed Solution: Question 3

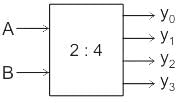

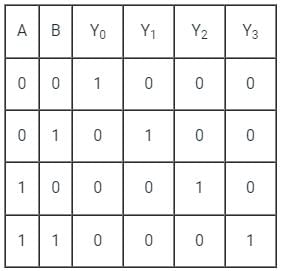

In a decoder, if the input lines are 4 then number of maximum output lines will be:

Detailed Solution: Question 4

How many 3 × 8 line decoders with an enable input line are needed to construct a 6 × 64 line decoder without using any other logic gate?

Detailed Solution: Question 5

Direction: Given question consists of two statements, one labeled as the 'Assertion (A)' and the other as 'Reason (R)'. You are to examine these two statements carefully and select the answers to these items using the codes given below.

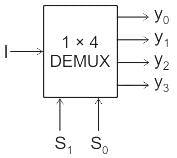

Assertion (A): A de-multiplexer cannot be used as a decoder.

Reason (R): A de-multiplexer selects one of many outputs, whereas a decoder selects an output corresponding to the coded input.

Detailed Solution: Question 6

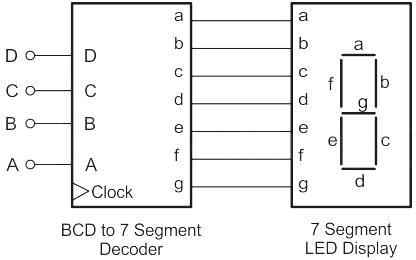

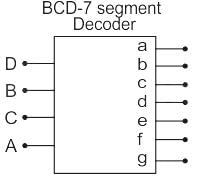

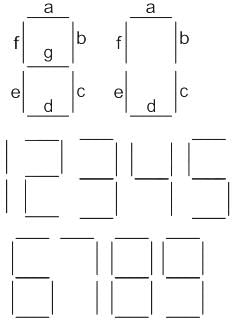

The number of input lines in a common BCD to seven segment decoder is _____.

Detailed Solution: Question 7

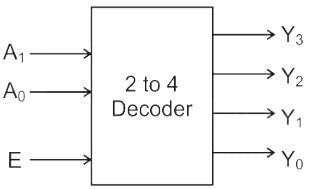

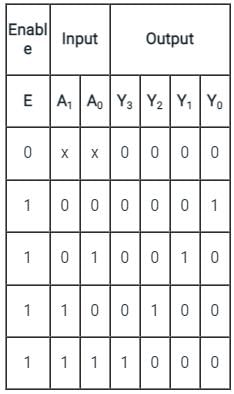

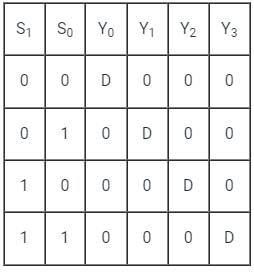

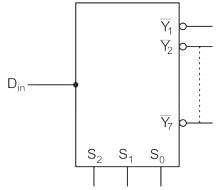

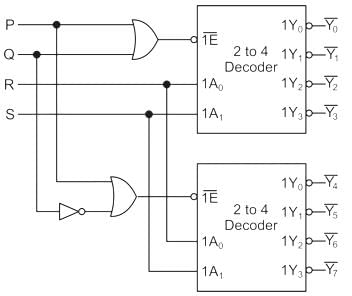

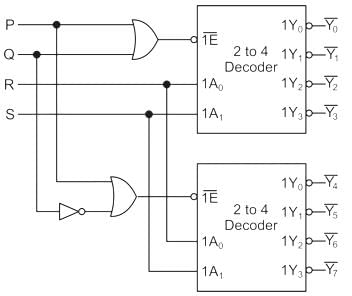

A 1 to 8 demultiplexer with data input Din, address inputs S0, S1, and S2, (with S0 as the LSB) and Y̅0 to Y̅ 7 as the eight de-multiplexed output, is to be designed using two 2 to 4 decoders (with enable input E and address input A0 and A1) as shown in the figure. Din, S0, S1, and S2 are to be connected to P, Q, R, and S but not necessarily in this order. The respective input connections to P, Q, R, and S terminals should be

Detailed Solution: Question 8

Find the number of 2 × 1 MUX (multiplexers) required to implement 16 × 1 MUX.

Detailed Solution: Question 9

Detailed Solution: Question 10

Detailed Solution: Question 11

Detailed Solution: Question 12

Detailed Solution: Question 13

Detailed Solution: Question 14

Which of the following represents a number of output lines for a decoder with 4 input lines?

Detailed Solution: Question 15

26 docs|247 tests |