Test: Realization of Logic Gates - Electronics and Communication Engineering (ECE) MCQ

10 Questions MCQ Test - Test: Realization of Logic Gates

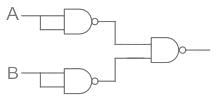

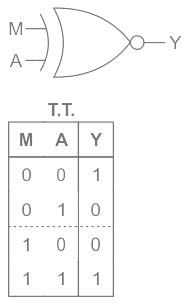

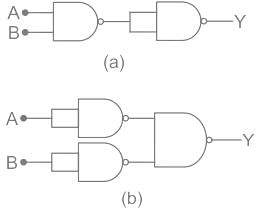

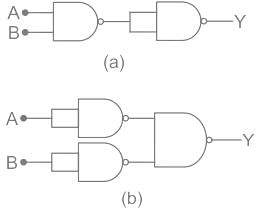

Above are the circuits that consist of NAND gates. Determine the logic operation carried out by these circuits?

The input to a logic gate is A = 1100 and B = 1010. What will be the output, if the logic gate is NAND gate?

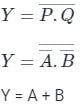

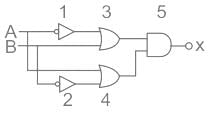

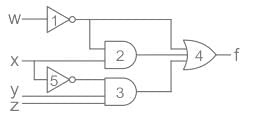

Consider the following gate network:

which gate is redundant

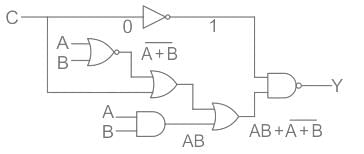

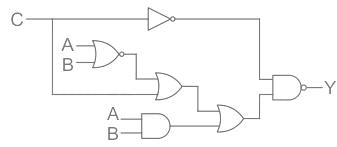

In the circuit shown in the figure, if C = 0, the expression for Y is

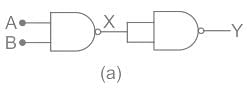

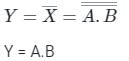

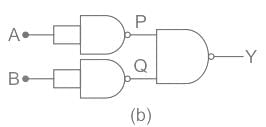

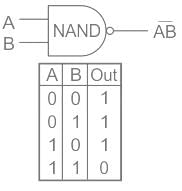

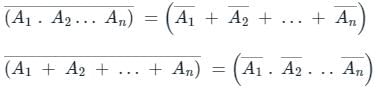

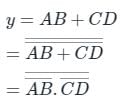

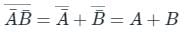

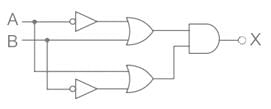

Determine the Boolean function of the following circuit.

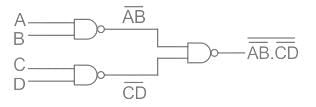

The Boolean function Y = AB + CD is to be realized using only 2 input NAND gates. The minimum number of gates required is

In an all NOR gate realization of a combinational circuit all EVEN and ODD level gates behave like

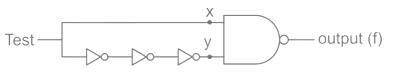

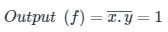

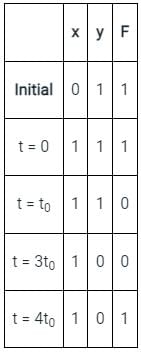

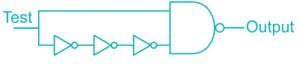

Consider the logic circuit with input signal TEST shown in the figure. All gates in the figure shown have identical non-zero delay. The signal TEST which was at logic LOW is switched to logic HIGH and maintained at logic HIGH. The output

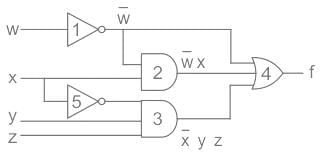

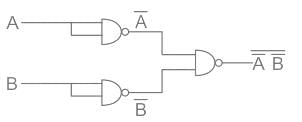

The output equivalent circuit of following circuit is