Test: Combinational Logic Circuits- 2 - Railways MCQ

20 Questions MCQ Test - Test: Combinational Logic Circuits- 2

Consider the following statements:

1. A decoder with a data input is called a demultiplexer.

2. An octal decoder with active-LOW outputs will output seven LOWs and one HIGH for each combination of inputs.

3. A hexadecimal decoder is sometimes called a 4-line-to-10-line decoder.

4. The Gray code is not a BCD-type code.

Which of the statements given above are not correct?

1. A decoder with a data input is called a demultiplexer.

2. An octal decoder with active-LOW outputs will output seven LOWs and one HIGH for each combination of inputs.

3. A hexadecimal decoder is sometimes called a 4-line-to-10-line decoder.

4. The Gray code is not a BCD-type code.

Which of the statements given above are not correct?

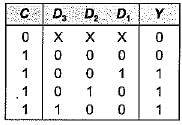

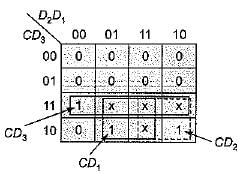

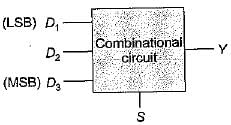

The combinational circuit shown below has three data lines D1, D2,and D3 while one select line S.

When the control line is high, the circuit is to detect when one of the data lines has ‘1’ on it. No more than one data line will ever have '1' on it. When the control line is low, the circuit will output ‘O’, regardless of what is on the data lines. The output Y of the combinational circuit will be:

When the control line is high, the circuit is to detect when one of the data lines has ‘1’ on it. No more than one data line will ever have '1' on it. When the control line is low, the circuit will output ‘O’, regardless of what is on the data lines. The output Y of the combinational circuit will be:

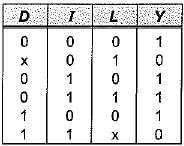

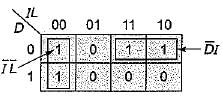

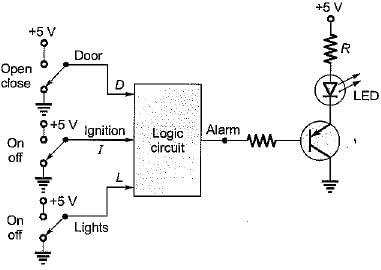

Figure below shows an automobile alarm circuit used to detect certain undesirable conditions. The three switches are used to indicate the status of the door by the driver’s seat, the ignition and the head lights, respectively.

What is the output of the above logic circuit with these three switches (D, I and L) as inputs so that the alarm will be activated whenever either of the following condition exists:

The headlights are ON while the ignition is OFF.

The door is open while the ignition is ON.

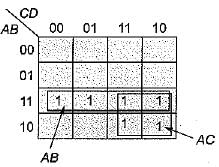

A logic circuit takes 4-BCD inputs {A, B, C and D) to give an output F. Output F is '1' if the input is an invalid BCD-code. The number of two input NAND gates required to implement the output Y is

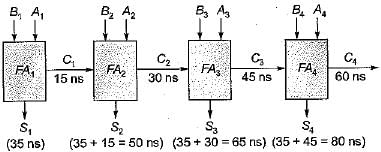

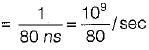

A 1-bit full adder takes 15 ns to generate carry out bit while 35 ns for the sum bit. If we design a 4-bit adder using cascade connection of four 1-bit full-adder, then the maximum number of additions that can be performed by this 4-bit adder will be:

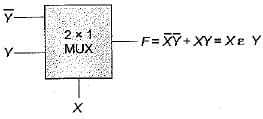

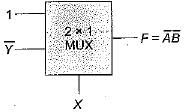

The number of two-input multiplexers required to implement an EX-NOR and a NAND gate are respectively

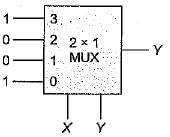

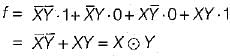

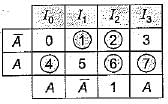

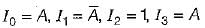

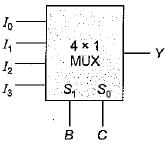

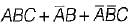

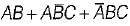

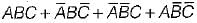

The logic expression f(A, B, C) = πM (0, 3,5) is required to be implemented using a 4 x 1 MUX as shown below.

The combinations of the input to this 4 x 1 MUX circuit would be

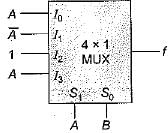

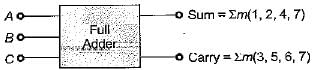

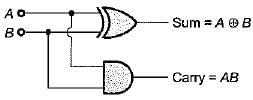

A full adder circuit can be implemented using:

1. One 3 x 8 decoder and two OR gates.

2. One 3 x 8 decoder, one OR gate and a NOT gate.

3. Two half adders and one OR gate.

4. Two half adders and one NOT gate.

5. Nine NAND/NOR gates.

6. 6 NAND/NOR gates.

Select the correct code from the given options.

To add two 4-bit numbers using parallel adder circuit we require

A combinational circuit has three inputs namely A, B and C (A being MSB and C being LSB).

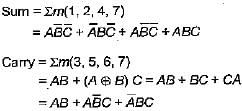

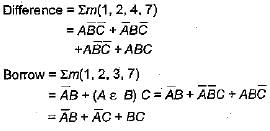

Match List-I (Combinational Circuit outputs) with List-II (Logic expressions) and select the correct answer using the codes given below the lists:

List-I

A. Full adder carry output

B. Full subtractor borrow output

C. Sum output of full adder or difference output of full subtractor

List-II

1.

2.

3.

Codes:

A B C

(a) 2 1 3

(b) 1 2 3

(c) 1 3 2

(d) 2 3 1

The correction to be appiied in decimal adder to the generated sum is

The gates required to build a half adder are:

The code where all successive numbers differ from their preceding number by single bit is

A device which changes from serial data to parallel data is

A device which converts BCD to Seven Segment is called

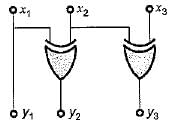

The logic circuit shown below converts a binary code x1 x2 x3 into

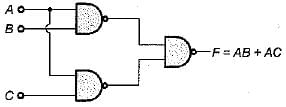

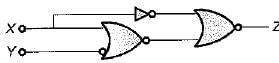

The logic circuit shown below can be minimized to

When the set of input data to an even parity generator is 0111, the output will be