Combinational Logic - Free MCQ Practice Test with solutions, GATE EE Digital

MCQ Practice Test & Solutions: Test: Combinational Logic (10 Questions)

You can prepare effectively for Electrical Engineering (EE) Digital Electronics with this dedicated MCQ Practice Test (available with solutions) on the important topic of "Test: Combinational Logic". These 10 questions have been designed by the experts with the latest curriculum of Electrical Engineering (EE) 2026, to help you master the concept.

Test Highlights:

- - Format: Multiple Choice Questions (MCQ)

- - Duration: 30 minutes

- - Number of Questions: 10

Sign up on EduRev for free to attempt this test and track your preparation progress.

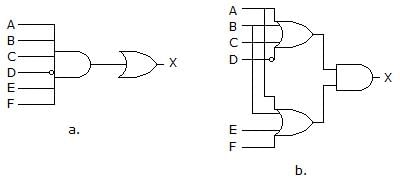

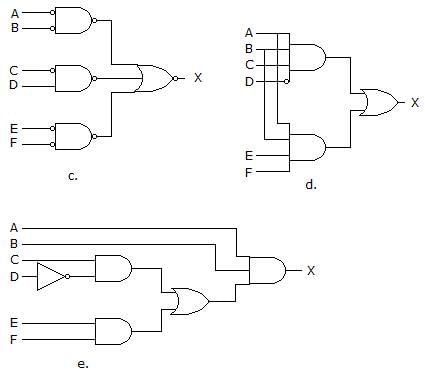

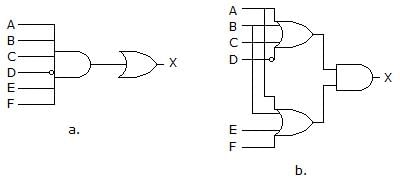

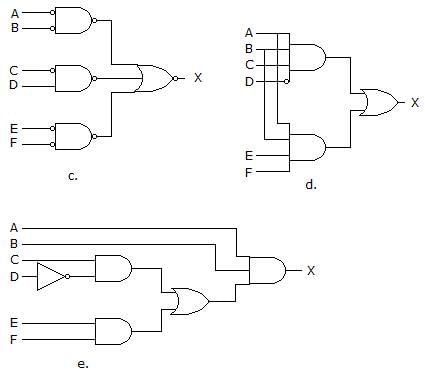

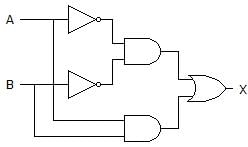

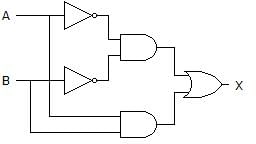

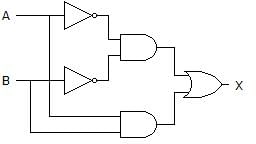

Which of the circuits in figure (a to d) is the sum-of-products implementation of figure (e)?

Detailed Solution: Question 1

Detailed Solution: Question 2

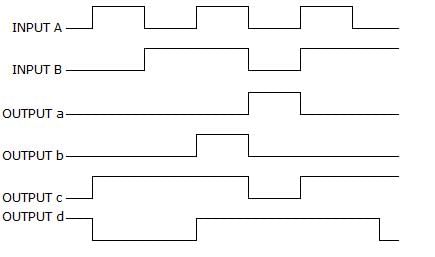

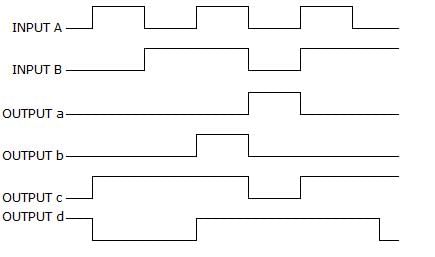

For a two-input XNOR gate, with the input waveforms as shown below, which output waveform is correct?

Detailed Solution: Question 3

What is the indication of a short to ground in the output of a driving gate?

Detailed Solution: Question 4

Detailed Solution: Question 5

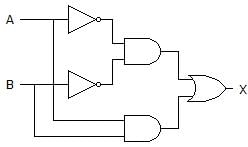

Which of the following logic expressions represents the logic diagram shown?

Detailed Solution: Question 6

What type of logic circuit is represented by the figure shown below?

Detailed Solution: Question 7

Which of the following combinations of logic gates can decode binary 1101?

Detailed Solution: Question 8

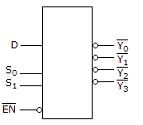

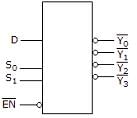

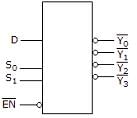

For the device shown here, assume the D input is LOW, both S inputs are LOW and the input is LOW. What is the status of the Y’ outputs?

Detailed Solution: Question 9

Detailed Solution: Question 10

113 videos|91 docs|58 tests |