Test: Sequential Circuits - 1 - Electrical Engineering (EE) MCQ

10 Questions MCQ Test - Test: Sequential Circuits - 1

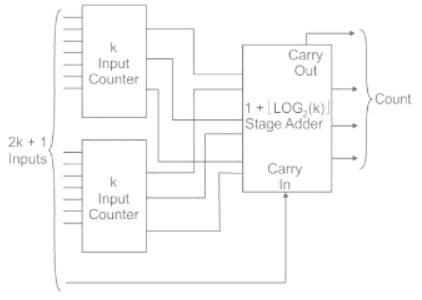

The expression for MOD number for a ripple counter with N flip-flops is

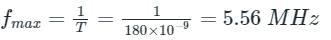

Calculate the maximum clock frequency at which a 4-bit asynchronous counter can work reliably. Assume the propagation delay of each flip-flop to be 40 ns and the width of the strobe pulse to be 20 ns.

A cascade of three identical modulo-5 counters has an overall modulus of

A shift register with its complement output (Q’) of the last stage connected to the D-input of the first stage is called:

A 4-bit synchronous counter uses flip-flops with a propagation delay time of 15 ns each. The maximum possible time required for change of state will be

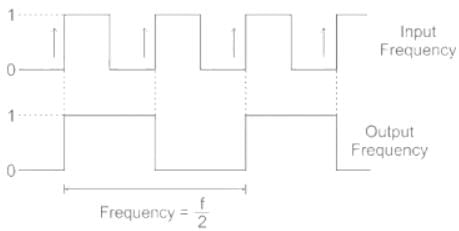

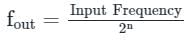

If the input to a T flip-flop is a 100 MHz signal, the final output of three T flip-flops in a cascade is

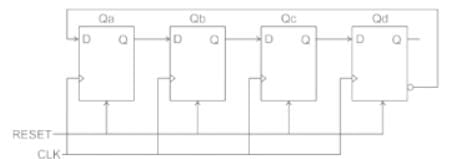

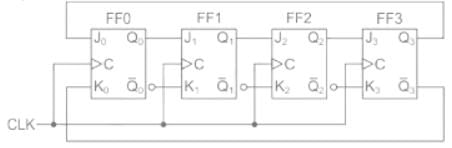

A Shift register in which the output of the last flip-flop is connected to the input of the first flip-flop

A 6 bit counter is used to count from 0, 1, 2, ......n. The value of n is _____

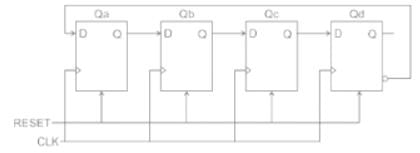

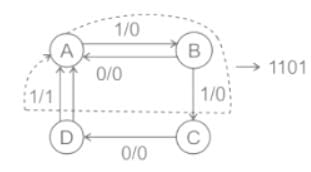

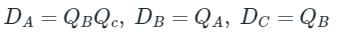

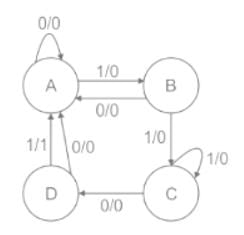

The sequence detected by the state diagram shown below is

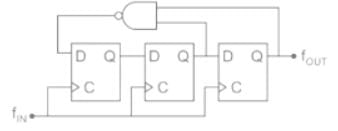

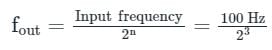

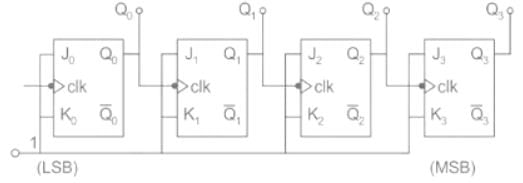

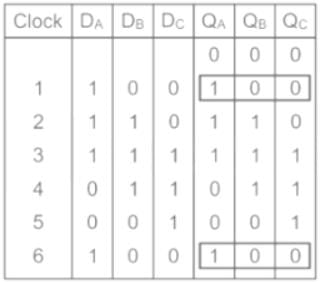

Which one of the following statements is true about the digital circuit shown in the figure?