Test: Cache & Main Memory- 2 - Computer Science Engineering (CSE) MCQ

15 Questions MCQ Test Question Bank for GATE Computer Science Engineering - Test: Cache & Main Memory- 2

A system which has lot of crashes, data should be written to the disk using

The average memory access time for a machine with a cache hit rate of 90% where the cache access time is 10 ns and the memory access time is 100 ns is

Given below are some statements associated with cache memory. Identify the correct statement.

Which of the following holds data and processing instructions temporarily until the CPU needs it?

Suppose a cache is 10 times faster than main memory and suppose that the cache can be used 70% of the time. How much speed up do we gain by using the cache?

Given below are some statements associated with computer memory. Identify the correct statement.

In a two level memory hierarchy, the access time of the cache memory is 12 nsec and the access time of the main memory is 1.5 msec. The hit ratio is 0.98. What is the average access time of the two level memory system?

Determine True(T) / False(F) of the following statements.

1. Dynamic RAM consists of internal flip-flops.

2. Static RAM consists of capacitors.

3. Static RAM is easier to use than dynamic RAM.

4. Static RAM has shorter read and write cycles than that of dynamic RAM

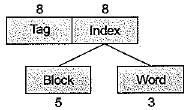

Consider the following organization of main memory and cache memory:

Main memory: 64K x 16

Cache memory; 256 x 16

Memory is word-addressable and block size is of 8 words. Determine the size of tag field if direct mapping is used for transforming data from main memory to cache memory.

A certain computer system design has a single CPU, a two-level cache, and supports memory mapped I/O for output-only controllers. Which of the following is true?

The designer of a cache system need to reduces the number of cache misses that occur in a certain group of programs. Which of the following statements is/are true?

1. If compulsory misses are most common then the designers should consider increasing the cache line size to take better advantage of locality.

2. If capacity misses are most common then the designer should consider increasing the total cache size so it can contain more lines.

3. If conflict misses are most common then the designers should increasing the cache’s associativity, in order to provide more flexibility when collision occurs.

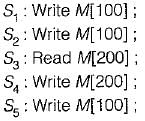

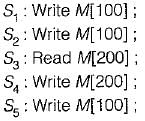

Assume a fully associative write-back cache with many cache entries that starts empty. We define a sequence of memory operations. The address or locations is in square brackets.

Q. What are the number of hits when using no write allocate versus write allocate?

Assume a fully associative write-back cache with many cache entries that starts empty. We define a sequence of memory operations. The address or locations is in square brackets.

Q. What are the number of misses when using no write allocate versus write allocate?

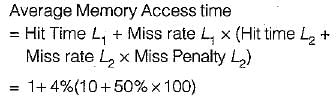

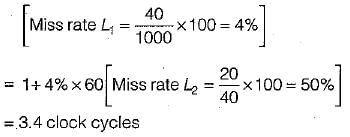

Suppose a CPU contains 1000 memory references there are 40 misses in L1 cache (First Level Cache) and 20 misses in the L2 cache (Second Level Cache). Assume miss penalty from the L2 cache to memory is 100 clock cycles the hit time of L2 cache is 10 clock cycles, the hit time of L1 cache is 1 clock cycle and there are 1.5 memory references per instruction.

Q. What is the average memory access time?

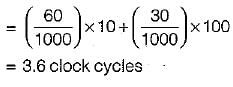

Suppose a CPU contains 1000 memory references there are 40 misses in L1 cache (First Level Cache) and 20 misses in the L2 cache (Second Level Cache). Assume miss penalty from the L2 cache to memory is 100 clock cycles the hit time of L2 cache is 10 clock cycles, the hit time of L1 cache is 1 clock cycle and there are 1.5 memory references per instruction.

Q. What is average memory stalls per instruction?

|

73 videos|8 docs|165 tests

|

|

73 videos|8 docs|165 tests

|