Gate Practice Test: Electrical Engineering(EE)- 10 - Electrical Engineering (EE) MCQ

30 Questions MCQ Test - Gate Practice Test: Electrical Engineering(EE)- 10

“Nobody praised her ________ nature, so she decided to mend her ways to become ________.”

The words that best fill the blanks in the above sentence are

“All the development programmes of the government have been ________ over the years by the perpetual rise in the population of the country.”

D = ABC + BCA + CAB where A, B and C are decimal digits, then D is divisible by

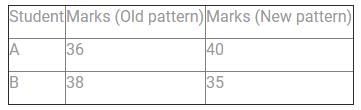

In an examination 100 questions of 1 mark each are given. After the examination, 20 questions are deleted from evaluation, leaving 80 questions with a total of 100 marks. Student A had answered 4 of the deleted questions correctly and got 40 marks, whereas student B had answered 10 of the deleted questions correctly and got 35 marks. In this situation,

Two solutions of X and Y containing ingredients A, B and C in proportions a : b : c and c : b: a, respectively are mixed. For the resultant mixture to have A, B and C in equal proportion. It is necessary that

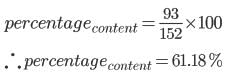

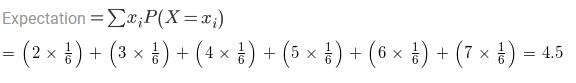

In the given diagram of Testbook team, contents are represented in the parallelogram, technical in the rectangle and DTP in the triangle. Out of the total number of the people, the percentage of content shall be in the range of ________.

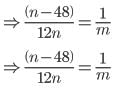

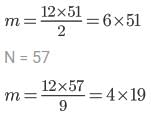

How many pairs of positive integers m, n satisfy 1/m + 4/n = 1/12 where n is an odd integer less than 60?

Most successful professional football players began playing football as youth, though a significant number learned the sport later in life. No professional football player who ignored the advice of his coaches, however, has ever become successful. If the statements are true, which of the following must also be true?

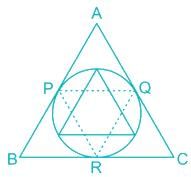

The diagram shows a circle with one equilateral triangle inside and one equilateral triangle outside. The ratio of areas of big triangle to the small triangle is n :1. Find the value of n.

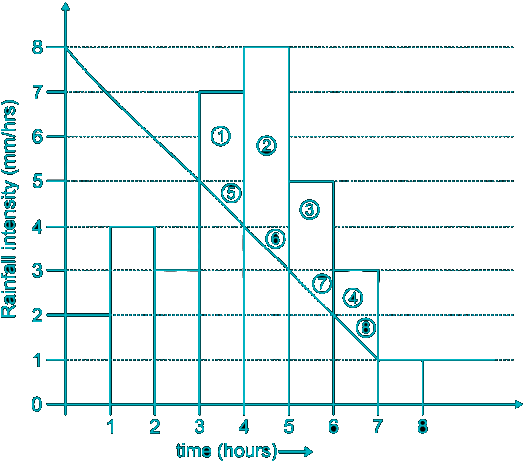

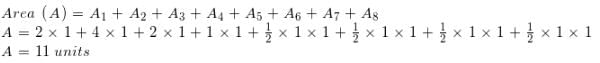

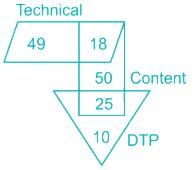

The following hydrograph depicts the rainfall intensity of an area for the time period of 8 hours. Also, infiltration curve is plotted on the same graph for the given land characteristics. Hydrograph region below the infiltration curve represents infiltrated portion of rainfall. Calculate the excess of rainfall occurred.

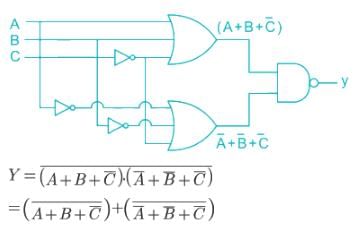

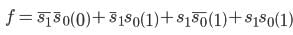

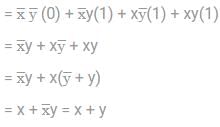

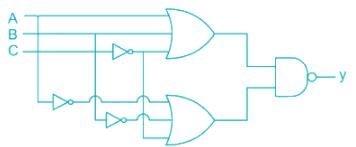

Which of the following expression represents the given logic circuit?

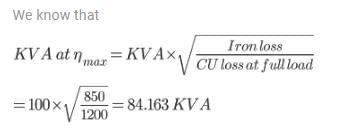

A Transformer is rated at 100 KVA. At full load its copper loss is 1200 W and its iron loss is 850 W. Calculate the load (in KVA) at which maximum efficiency will occur.

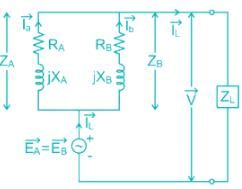

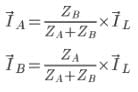

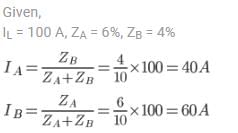

Two transformers operating in parallel having impedance of 6 % and 4 %. If the total load supplied by the combinations is 100 A, then the current supplied by 6 % impedance transformer _______ A.

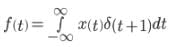

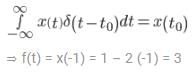

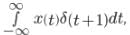

Let x(t) = 1 – 2t. Then what is the value of  where δ(t + 1) is unit impulse at t = -1.

where δ(t + 1) is unit impulse at t = -1.

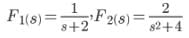

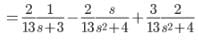

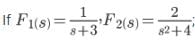

what is the inverse Laplace transform of the product F1(s) . F2(s)?

what is the inverse Laplace transform of the product F1(s) . F2(s)?

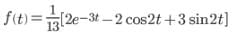

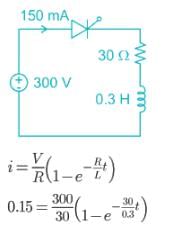

Latching current for an SCR, inserted in between a dc voltage source of 300 V and the load, is 150 mA. Compute the minimum width of gate pulse current required to turn-on this SCR in case the load of L = 0.3 H in series with R = 30 Ω

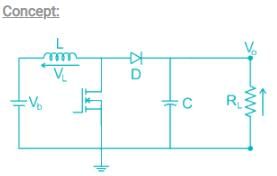

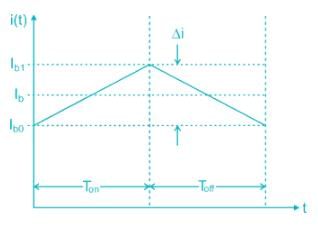

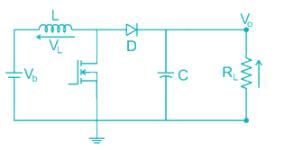

A step-up chopper shown in figure is to deliver 3A

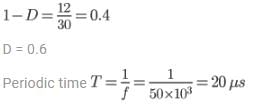

In to the 10 Ω load. The battery voltage is 12 V, L = 20 μH, C = 100 μF and chopper frequency is 50 kHz. Determine the on-time of the chopper ________ μs

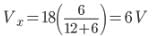

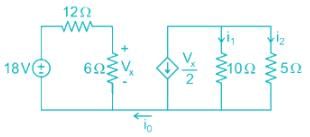

For the circuit, shown in the figure below, the values of i0 and i1 respectively are

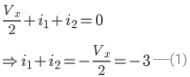

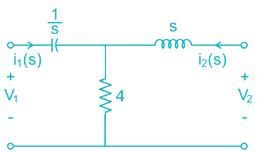

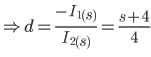

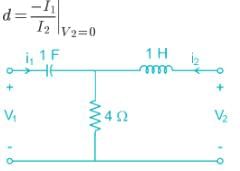

For the two – port circuit shown in the figure, the S – domain expression for the parameter d is where

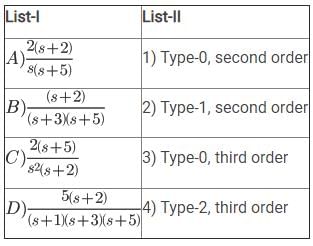

Match List-I (Transfer function of the system) with List-II (Type and order of the system) and select the correct answer using the codes given below the Lists:

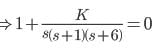

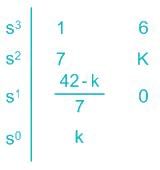

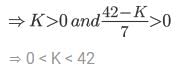

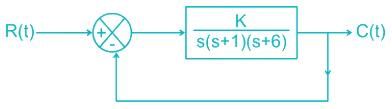

The feedback system shown below is stable for all values of K given by

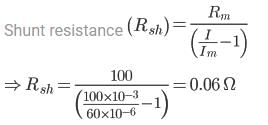

A 60 μA meter has a resistance of 100 ohms. If the meter has to measure 100 mA, then the value of shunt resistance and the current through shunt respectively are

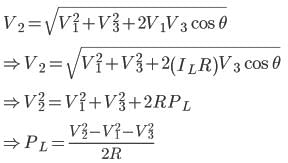

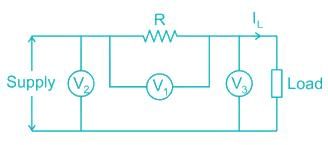

In the measurement of power by 3 voltmeter method connected as shown below. The expression for power consumed in the load is given by

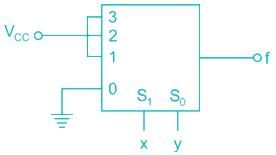

The output of the 4 to 1 MUX shown in the below figure is

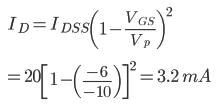

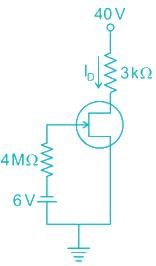

Find VDS under DC condition of the given circuit

Given rd = 15 KΩ, IDSS = 20 mA, Vp = -10V

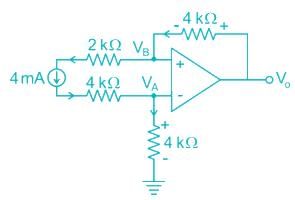

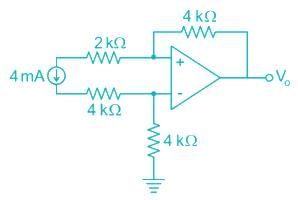

What is the output voltage Vo (in Volt)of the given circuit?

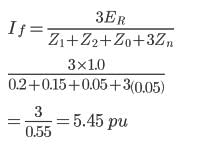

A 30 kV, 50 Hz, 60 MVZ generator has the positive negative and zero sequence reactance of 0.2 pu, 0.15 pu and 0.05 pu respectively. The generator ground with a reactance of 0.05 pu. The fault current magnitude for a single line to ground fault is ________(in pu)

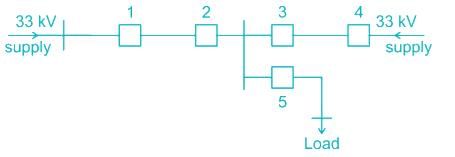

The distribution system shown in the figure is to be protected by over current system of protection. For proper fault discrimination, directional over current relays will be required at which locations?

In a four-bus system the total self-admittance of bus 2 is Y22 = -j14 p.u. A transmission line having a series reactance of j 0.2 p.u. and shunt capacitance of j 0.5 p.u. is connected between buses 2 and 3. The magnitude value of y22 modified is________

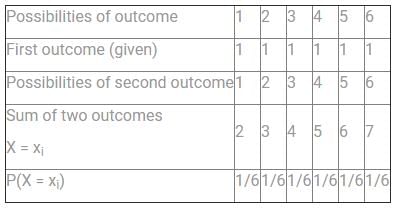

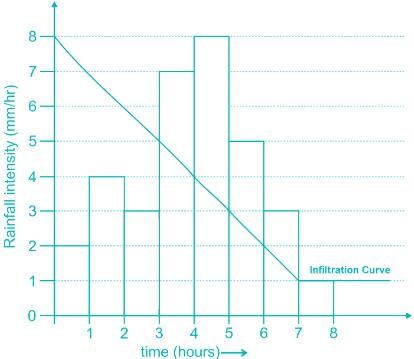

A fair die is rolled two times independently. Given that the outcome on the first roll is 1, the expected value of the sum of the two outcomes is