Test: Sequential Circuits - 2 - Electrical Engineering (EE) MCQ

15 Questions MCQ Test Analog and Digital Electronics - Test: Sequential Circuits - 2

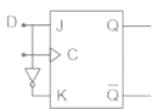

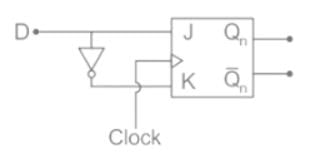

In a J-K flip-flop, if J = K̅, then it acts as a/an:

A pulse train with a frequency of 1 MHz is counted using a mod-1024 ripple counter built with J-K flip-flops. For proper operation of the counter the maximum permissible propagation delay per flip-flop stage is

Three T flip flops are connected to form a counter. The maximum states possible for the counter will be:

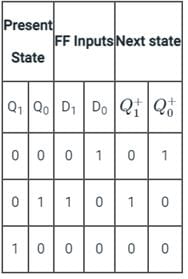

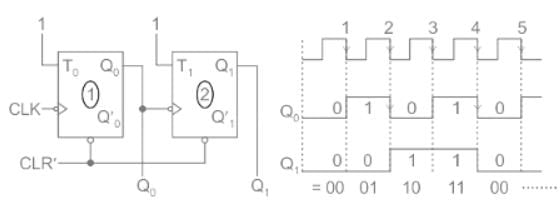

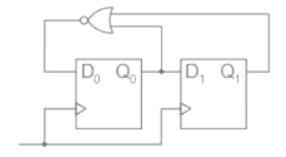

For the circuit shown, the counter state (Q1Q0) follows the sequence

An eight-bit binary ripple UP counter with a modulus of 256 is holding the count 01111111. What will be the count after 135 clock pulses?

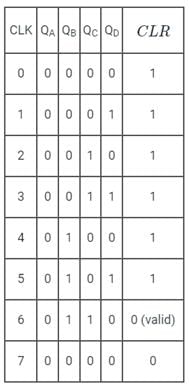

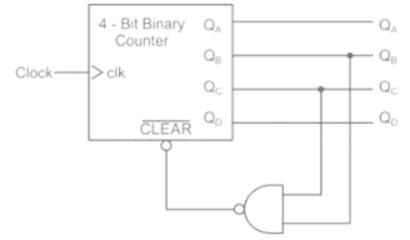

A mod–n counter using a synchronous binary up–counter with synchronous clear input is shown in the figure. The value of n is_________.

(Important - Enter only the numerical value in the answer)

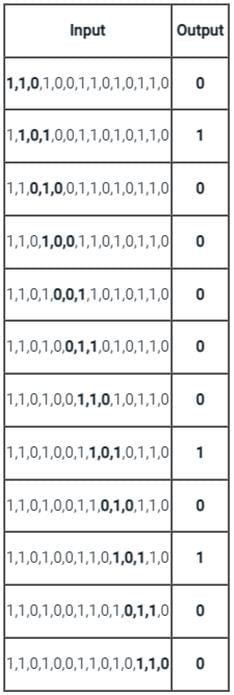

A sequence detector is designed to detect precisely 3 digital inputs, with overlapping sequences detectable. For the sequence (1,0,1) and input data (1,1,0,1,0,0,1,1,0,1,0,1,1,0), what is the output of this detector?

Which of the following is not a sequential circuit?

A __________ counter can be implemented using three flipflops.

If the 5-bit ripple counter and 5-bit synchronous counter are having flip-flops with a propagation delay of 20 ns, the maximum delay in the ripple counter (x) and synchronous counter (y) will be:

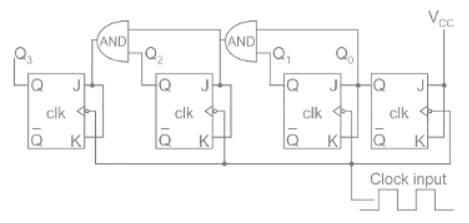

For the following cascaded Counters find the value of X of the mode-X counter.

(Important - Enter only the numerical value in the answer)

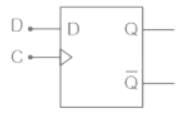

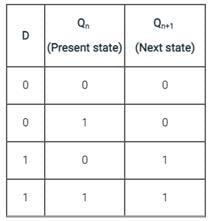

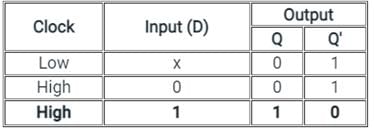

In a D flip flop, if the present state is 1, what will be the next state of the output at the complement end?

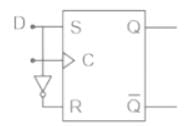

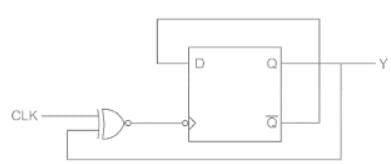

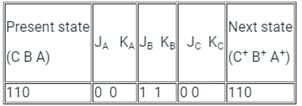

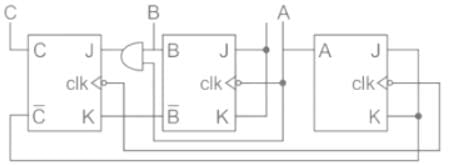

A three-bit counter arrangement is shown below. It ig given that the counter was initially 000 (C B A) Determine its count sequence for next pulses and also determine whether the counter is self-starting.

|

137 videos|144 docs|71 tests

|