Logical (Virtual) Vs Physical Address Space

Memory Allocation Techniques

To store data and to run processes efficiently, a computer system needs sufficiently large memory with fast access. Increasing memory size can increase access time and complicate address handling. The CPU generates addresses as if for a single contiguous address space (these are logical addresses), while the physical storage resides in main memory. Therefore, an address translation mechanism is required to convert logical (virtual) addresses produced by the CPU into actual physical addresses used by main memory.

Main memory interacts with both user processes and the operating system. The OS must manage this memory so that processes have the memory they need while CPU memory accesses remain fast. Main memory is often viewed as divided into non-overlapping regions called partitions.

The main memory can be broadly allocated in two ways:

- Contiguous memory allocation

- Non-contiguous memory allocation

Contiguous memory allocation

In contiguous allocation, each process occupies one continuous block of physical memory. This approach simplifies address translation and protection but can cause inefficient use of memory (fragmentation).

Contiguous allocation can be categorised as:

- Fixed partition scheme

- Variable partition scheme

Partition allocation within contiguous schemes commonly uses these placement strategies:

- First Fit

- Best Fit

- Worst Fit

- Next Fit

Non-contiguous memory allocation

In non-contiguous allocation, a process may occupy several separate frames or segments in physical memory. This reduces external fragmentation and allows better use of available memory but requires more complex address translation and additional data structures.

Common non-contiguous techniques are:

- Paging

- Multilevel paging

- Inverted paging

- Segmentation

- Segmented paging

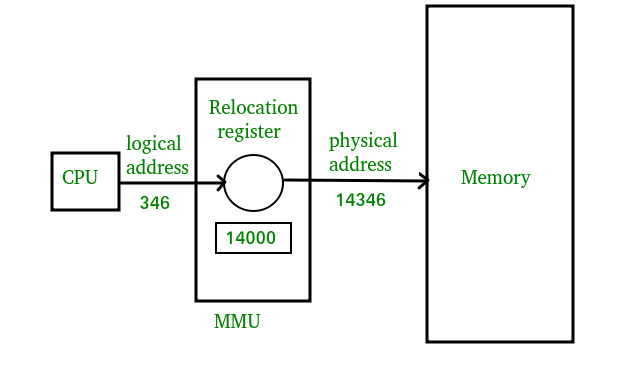

Memory-Management Unit (MMU)

The run-time mapping between a virtual address and a physical address is performed by a hardware device called the Memory-Management Unit (MMU). The operating system provides data structures and control to the MMU to implement mapping, protection and sharing.

The typical connection is:

CPU → MMU → Memory

The MMU performs translation for every memory reference from the CPU. Example of a simple relocation scheme:

- CPU generates a logical address, for example: 346

- MMU supplies a relocation (base) register value, for example: 14000

- Physical address is computed as: 346 + 14000 = 14346

The relocation value is added to each logical address produced by a user process before the address is used to access main memory. The user program itself never sees the real physical addresses; it works with logical addresses (for instance, it may create and compare pointers like 346), while the MMU ensures they refer to actual memory locations.

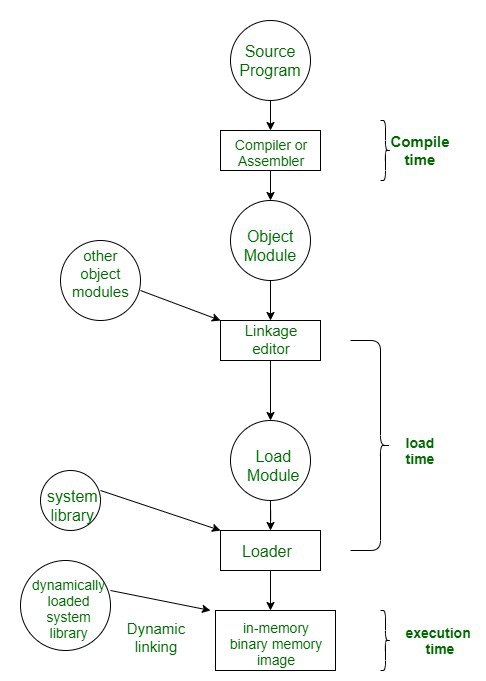

Address Binding

Address binding is the process of mapping addresses from one address space to another. A logical address (also called virtual address) is generated by the CPU while a program executes. A physical address identifies a location in main memory (RAM). The MMU or binding mechanism translates logical addresses to physical addresses so that the CPU can access the required data or instructions in memory.

An address binding can occur at three different times:

- Compile time: If it is known where a process will reside in memory at compile time, the compiler can generate absolute addresses (physical addresses embedded in the executable). Loading the program to the expected location is fast because no relocation is needed. The drawback is lack of flexibility: if the chosen physical area is occupied, the program must be recompiled or cannot run.

- Load time: If the final physical location is not known at compile time but will be fixed at load time, the compiler generates relocatable addresses. The loader adds the process base address to these relocatable addresses to produce absolute addresses. If the loader later places the process at a different base, the program must be reloaded (relocated) again.

- Execution time: If the process may move during execution (for example, the OS swaps the process out and later back into a different area), binding must be delayed until run-time. This requires hardware support (for example, an MMU with base/limit or page tables). Dynamic linking and dynamic relocation are examples of run-time binding. Example: compaction-moving a process in memory to reduce fragmentation is possible only when addresses are translated at run-time.

Mapping Virtual Addresses to Physical Addresses

In contiguous allocations the mapping is straightforward: if a process is loaded starting at physical base address B, then a logical address L maps to physical address P = B + L, provided L is within the process limit. Thus knowing the base (and limit) is sufficient to compute the physical address.

For non-contiguous allocation the mapping is more complex. Examples of structures used for mapping include page tables (for paging), multi-level page tables, inverted page tables, and segment tables (for segmentation). These techniques require additional hardware support for fast translation, such as a Translation Lookaside Buffer (TLB) to cache recent translations.

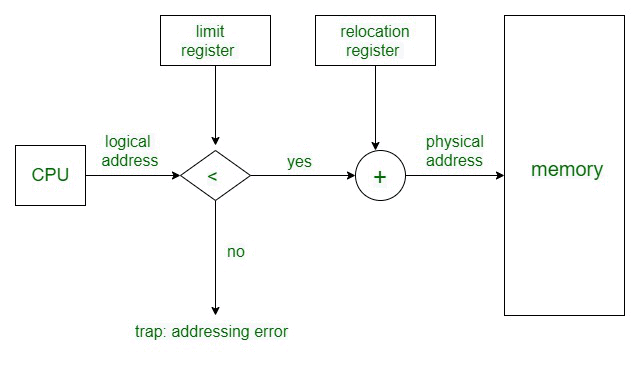

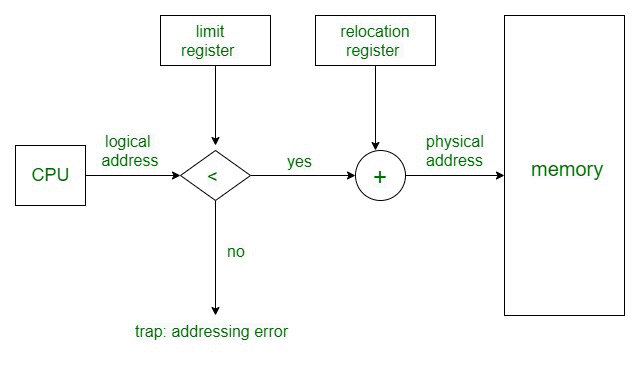

MMU registers

The MMU commonly uses two registers to implement simple relocation and protection:

- Base register (relocation register): contains the physical starting address of the process in memory.

- Limit register: contains the size (limit) of the process address region relative to the base.

When the CPU generates a logical address L, the MMU first checks whether L < limit. If so, the physical address is computed as base + L. If L ≥ limit, the MMU signals a memory protection violation (trap) to the operating system and the process is typically terminated or an error handler is invoked. This combination of base and limit provides both dynamic relocation and protection against illegal memory access.

Non-Contiguous Address Translation Brief Overview

Non-contiguous techniques handle address translation without requiring the process to occupy a single continuous block:

- Paging: The logical address is divided into a page number and an offset. The page number indexes into a page table to find the corresponding physical frame; the offset is added within that frame. Page tables can be large and are often kept in main memory; a TLB caches recent page-table entries for speed.

- Multilevel paging: Page tables are arranged in levels to reduce memory used for page tables. The logical page number is split into indices for each level.

- Inverted paging: Instead of a per-process page table, the system keeps a single table indexed by physical frame number that records which process and which virtual page maps to that frame-saving space at the cost of complicating lookups.

- Segmentation: The logical address is a pair (segment number, offset). Each segment has its own base and limit; segments correspond to logical program units such as code, stack or heap.

- Segmented paging: Combines segmentation and paging to get benefits of both: segmentation for logical program structure and paging within each segment to avoid external fragmentation.

All non-contiguous schemes require careful hardware and OS support for translation, protection and efficient implementation (for example, use of TLBs, page-replacement algorithms, and representation of page tables).

Logical and Physical Address

Logical address: generated by the CPU while a program runs. It is a virtual address and does not correspond directly to a physical memory location. The collection of logical addresses that a program can generate is called the logical address space or virtual address space.

Physical address: identifies a real memory location in RAM. The user program cannot directly access physical addresses; the MMU and OS map logical addresses to physical addresses before memory is accessed. The collection of physical addresses that correspond to a logical address space is the physical address space.

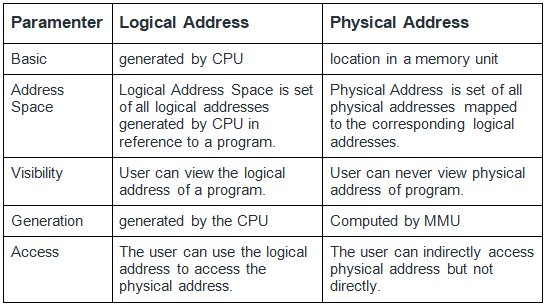

Differences Between Logical and Physical Addresses

- Generation: A logical address is generated by the CPU while a program executes; a physical address denotes an actual location in memory.

- Computation: Logical addresses are produced by the program; physical addresses are computed by the MMU (using base/limit, page tables, etc.).

- Existence: Logical addresses are virtual and do not exist physically until mapped; physical addresses are actual memory locations.

- Access: The logical address is used as a reference to access the physical address; physical addresses are not directly used by user programs.

- Visibility: Users and programs can reason about logical addresses; physical addresses are normally hidden from user programs for protection and portability.

- Address space: The set of logical addresses for a program is the logical address space; the set of physical addresses that those logical addresses map to is the physical address space.

Additional Concepts and Practical Points

- Fragmentation: Contiguous allocation suffers from external fragmentation (free blocks scattered) and possibly internal fragmentation (unused space inside allocated blocks). Paging eliminates external fragmentation but may cause internal fragmentation within the last page of a process.

- Compaction: In contiguous allocation, compaction moves allocated regions to coalesce free space and reduce external fragmentation. Compaction requires run-time address translation (base/limit or other dynamic mapping).

- Protection and sharing: Base/limit registers provide simple protection. Page tables and segment tables support finer-grained protection and sharing of code or data between processes.

- Translation Lookaside Buffer (TLB): A small hardware cache that stores recent logical-to-physical translations to speed up address translation. TLB hits are fast; misses require a page-table lookup.

- Virtual memory: Extends the logical address space beyond physical memory by keeping parts of a process on secondary storage (disk) and bringing pages/segments into physical memory on demand. This relies on demand paging or demand segmentation and appropriate page-replacement algorithms.

Comparison Chart

The following figure summarises and compares logical and physical addressing concepts, and common translation schemes.

Summary

Logical (virtual) addresses are produced by programs and viewed by users; physical addresses are used by the memory hardware. The MMU and the operating system implement address binding and translation. Contiguous allocation uses simple base/limit relocation but can lead to fragmentation; non-contiguous allocation (paging, segmentation and variants) requires more complex translation mechanisms, but improves memory utilisation and supports virtual memory. Understanding how logical addresses map to physical addresses-through compile-time, load-time or execution-time binding and via hardware structures such as the MMU, page tables and TLB-is essential for memory management, protection and performance in modern operating systems.

| Explore Courses for Computer Science Engineering (CSE) exam |  |

| Get EduRev Notes directly in your Google search |  |