T flip flop | Digital Circuits - Electronics and Communication Engineering (ECE) PDF Download

Introduction

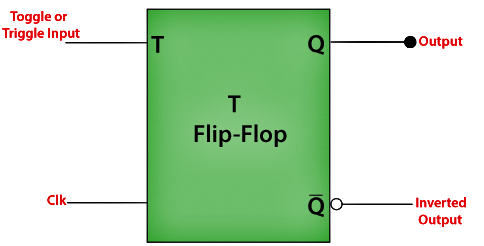

- In T flip flop, "T" defines the term "Toggle". In SR Flip Flop, we provide only a single input called "Toggle" or "Trigger" input to avoid an intermediate state occurrence. Now, this flip-flop work as a Toggle switch. The next output state is changed with the complement of the present state output. This process is known as "Toggling"'.

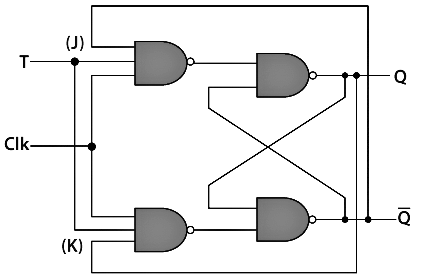

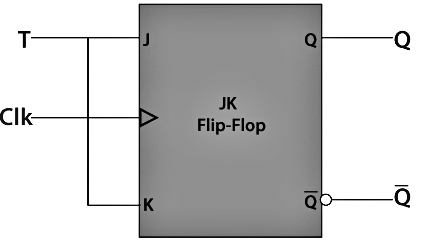

- We can construct the "T Flip Flop" by making changes in the "JK Flip Flop". The "T Flip Flop" has only one input, which is constructed by connecting the input of JK flip flop. This single input is called T. In simple words, we can construct the "T Flip Flop" by converting a "JK Flip Flop". Sometimes the "T Flip Flop" is referred to as single input "JK Flip Flop".

- Block diagram of the "T-Flip Flop" is given where T defines the "Toggle input", and CLK defines the clock signal input.

T Flip Flop Circuit

There are the following two methods which are used to form the "T Flip Flop":

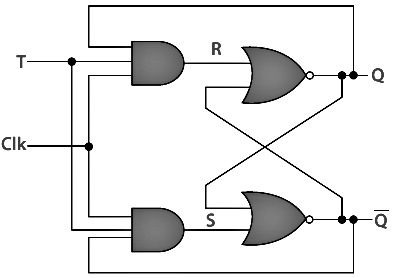

- By connecting the output feedback to the input in "SR Flips Flop".

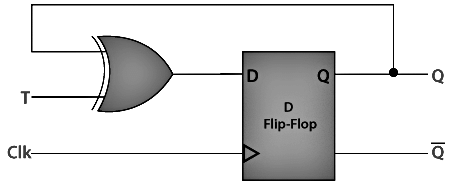

- We pass the output that we get after performing the XOR operation of T and QPREV output as the D input in D Flip Flop.

Construction

The "T Flip Flop" is designed by passing the AND gate's output as input to the NOR gate of the "SR Flip Flop". The inputs of the "AND" gates, the present output state Q, and its complement Q' are sent back to each AND gate. The toggle input is passed to the AND gates as input. These gates are connected to the Clock (CLK) signal. In the "T Flip Flop", a pulse train of narrow triggers are passed as the toggle input, which changes the flip flop's output state. The circuit diagram of the "T Flip Flop" using "SR Flip Flop" is given below:

The "T Flip Flop" is formed using the "D Flip Flop". In D flip - flop, the output after performing the XOR operation of the T input with the output "QPREV" is passed as the D input. The logical circuit of the "T-Flip Flop" using the "D Flip Flop" is given below:

The simplest construction of a D Flip Flop is with JK Flip Flop. Both the inputs of the "JK Flip Flop" are connected as a single input T. Below is the logical circuit of the T Flip Flop" which is formed from the "JK Flip Flop":

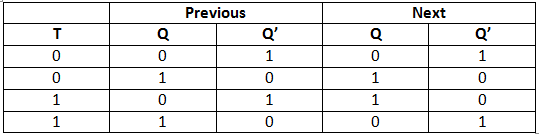

Truth Table of T Flip Flop

- The upper NAND gate is enabled, and the lower NAND gate is disabled when the output Q To is set to 0. make the flip flop in "set state(Q=1)", the trigger passes the S input in the flip flop.

- The upper NAND gate is disabled, and the lower NAND gate is enabled when the output Q is set to 1. The trigger passes the R input in the flip flop to make the flip flop in the reset state(Q=0).

Operations of T-Flip Flop

The next sate of the T flip flop is similar to the current state when the T input is set to false or 0.

- If toggle input is set to 0 and the present state is also 0, the next state will be 0.

- If toggle input is set to 0 and the present state is 1, the next state will be 1.

The next state of the flip flop is opposite to the current state when the toggle input is set to 1.

- If toggle input is set to 1 and the present state is 0, the next state will be 1.

- If toggle input is set to 1 and the present state is 1, the next state will be 0.

The "T Flip Flop" is toggled when the set and reset inputs alternatively changed by the incoming trigger. The "T Flip Flop" requires two triggers to complete a full cycle of the output waveform. The frequency of the output produced by the "T Flip Flop" is half of the input frequency. The "T Flip Flop" works as the "Frequency Divider Circuit."

In "T Flip Flop", the state at an applied trigger pulse is defined only when the previous state is defined. It is the main drawback of the "T Flip Flop".

The "T flip flop" can be designed from "JK Flip Flop", "SR Flip Flop", and "D Flip Flop" because the "T Flip Flop" is not available as ICs. The block diagram of "T Flip Flop" using "JK Flip Flop" is given below:

|

75 videos|145 docs|70 tests

|