NAND Gate PDF Download

Introduction

The NAND gate is a special type of logic gate in the digital logic circuit. The NAND gate is the universal gate. It means all the basic gates such as AND, OR, and NOT gate can be constructed using a NAND gate. The NAND gate is the combination of the NOT-AND gate. The output state of the NAND gate will be low only when all the inputs are high. Simply, this gate returns the complement result of the AND gate.

The logic or Boolean expression for the NAND gate is the complement of logical multiplication of inputs denoted by a full stop or a single dot as

(A.B)'=Y

The value of Y will be true when any one of the input is set to 0.

Types of Digital Logic AND Gate

The NAND gate is also classified into three types based on the input it takes. These are the following types of AND gate:

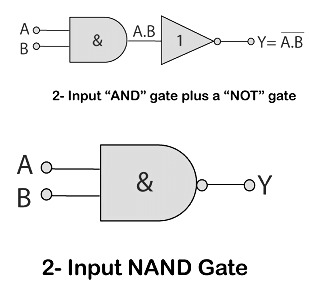

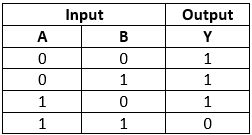

The 2-input NAND Gate

- This is the simple formation of the NAND gate. In this type of NAND gate, there are only two input values and an output value. There are 22=4 possible combinations of inputs. The truth table and logic design are given below:

Logic Design

Truth Table

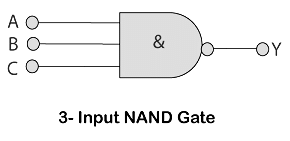

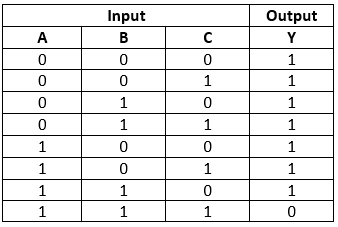

The 3-input NAND Gate

- Unlike the 2-input NAND gate, the 3-input NAND gate has three inputs. The Boolean expression of the logic NAND gate is defined as the binary operation dot(.). The NAND gate can be cascaded together to form any number of individual inputs. There are 23=8 possible combinations of inputs. The truth table and logic design are given below:

Logic Design

Truth Table

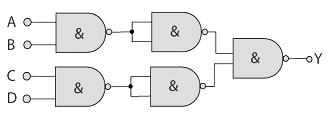

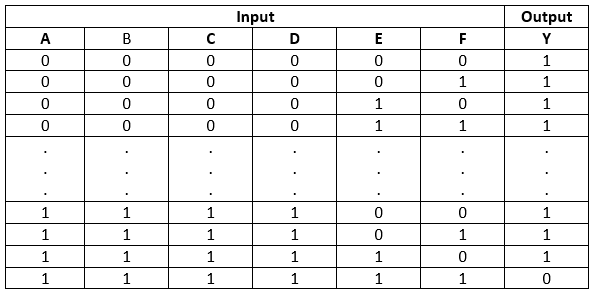

The Multi-input NAND Gate

Just like AND, NOT, and OR gate, we can also form n-input NAND gate. If the number of inputs required is odd, any "unused" input can be held high by directly connecting it to the power supply using high "suitable" pull-up resistors. There is the following expression of the 4-input NAND gate:

Y=((A.B).(C.D))'

In simple words, it is expressed as:

Y=A NAND B NAND C NAND D

Logic Design

Truth Table

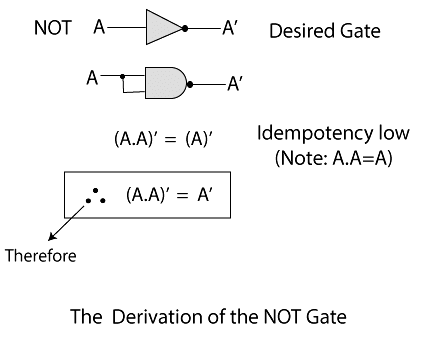

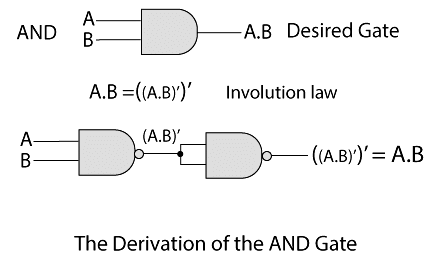

AND gate using NAND gate

|

Download the notes

NAND Gate

|

Download as PDF |

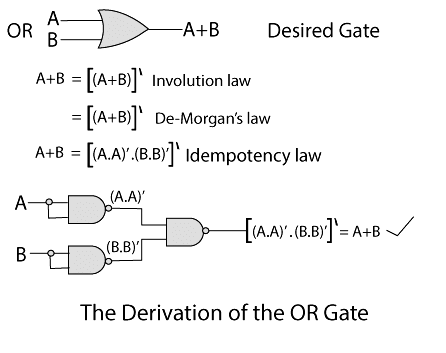

OR gate using NAND gate