Previous Year Questions: Interrupt | Computer Architecture & Organisation (CAO) - Computer Science Engineering (CSE) PDF Download

Q1: A keyboard connected to a computer is used at a rate of 1 keystroke per second. The computer system polls the keyboard every 10 ms (milli seconds) to check for a keystroke and consumes 100 μs (micro seconds) for each poll. If it is determined after polling that a key has been pressed, the system consumes an additional 200 μs to process the keystroke. Let T1 denote the fraction of a second spent in polling and processing a keystroke.

In an alternative implementation, the system uses interrupts instead of polling. An interrupt is raised for every keystroke. It takes a total of 1 ms for servicing an interrupt and processing a keystroke. Let T2 denote the fraction of a second spent in servicing the interrupt and processing a keystroke. The ratio T2/T1 is ______ . (Rounded off to one decimal place) (2023)

(a) 2.5

(b) 15.3

(c) 8.5

(d) 10.2

Ans: (d)

Sol: 1 Keystroke per second.

Polling System (T1)

CPU Polls (ask) keyboard every 10 ms and asks did you get any keystrokes.? Keyboard Answers “Yes” only once per second.

In One second, the CPU Polls the Keyboard 100 times (1 Sec = 1000 ms, and the CPU polls every 10 ms).

Time Spent in Polling = 100 * 100microsec = 10000 microseconds or 10 milesec.

Time Spent in Processing the Keystroke (Only once per second) = 200microsec or 0.2 milisec.

CPU’s Time wasted in Polling System = Time Spend in Polling + Time Spent in Processing = 10.2 ms

Interrupt System (T2)

CPU doesn’t ask Keyboard periodically about the keystroke, but Keyboard tells CPU via interrupt about a Keystroke.

Whenever, there is a keystroke, Keyboard interrupts CPU. CPU Executes corresponding Interrupt Service Routine (ISR) which takes 1ms. Thats all.

Speed Up of Interrupt over polling system (S) = T1/T2 = 10.2 ms / 1 ms = 10.2

Example:

Let's consider Rubina is personal assistant of Pathaan; Pathaan assigns some tasks to Rubina. Now Pathaan is a very busy man and his every minute is very important.

Pathaan needs the status of the work that he assigned to Rubina. Pathaan can take the status of the work in two ways:

Using Polling System

Using Interrupt System

If Pathaan uses Polling System, Pathaan will keep asking Rubina about the status of the work every 10 ms. 100 microsec of Pathaan are wasted in talking to Rubina, but Rubina answers Yes only once a second, If Rubina answer Yes then Pathaan spends another 200 microsec to review the work done by Rubina. So in this case Pathaan waste 100*100 microsec in talking to Rubina (Because he calls her every 10 ms and spends 100 microsec in talking so in one sec he waste 100*100 Microsec). Rubina completes work only once per second (Means she answers Yes only once out of 100 times that Pathaan asks in 1 sec). If Rubina answer Yes, Pathaan spends another 200 microsec to review the work done by Rubina. So Total time wasted by Pathaan is 10 ms + 0.2 ms.

Better approach will be : Pathaan Assign work to Rubina and sits back and wait for Rubina to tell him work is done. (Rubina Interrupts Pathaan). Rubina interrupts Pathaan once per second and Pathaan spends 1 ms in reviewing the work . (So Lots of time saved of Pathaan)

So, We can say second approach is 10.2 times faster than first approach.

Pathaan = CPU

Rubina = Input/Output.

Q2: Consider the following statements.

I. Daisy chaining is used to assign priorities in attending interrupts.

II. When a device raises a vectored interrupt, the CPU does polling to identify the source of interrupt.

III. In polling,the CPU periodically checks the status bits to know if any device needs its attention.

IV. During DMA, both the CPU and DMA controller can be bus masters at the same time.

Which of the above statements is/are TRUE? (2020)

(a) I and II only

(b) I and IV only

(c) I and III only

(d) III only

Ans: (c)

Sol: I is true

The daisy-chaining method of establishing priority consists of a serial connection of all devices that request an interrupt. The device with the highest priority is placed in the first position, followed by lower-priority devices up to the device with the lowest priority, which is placed last in the chain.

II. is false

Vectored interrupts are achieved by assigning each interrupting device a unique code, typically four to eight bits in length. When a device interrupts, it sends its unique code over the data bus to the processor, telling the processor which interrupt service routine to execute.

III. is true

The process of periodically checking status bits to see if it is time for the next I/O operation, is called polling. Polling is the simplest way for an I/O device to communicate with the processor the processor.

IV. is false

Since CPU release bus only after getting request from DMA and get after DMA release the BUS.

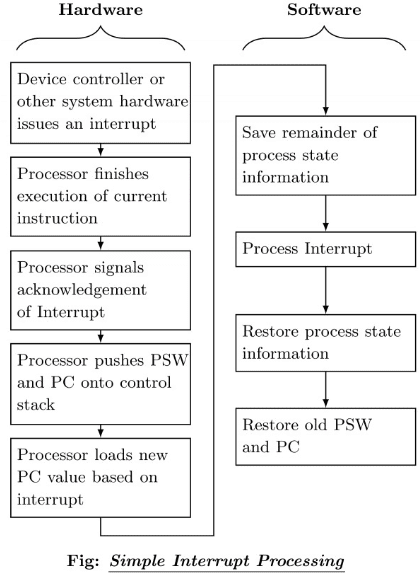

Q3: The following are some events that occur after a device controller issues an interrupt while process L is under execution.

(P) The processor pushes the process status of L onto the control stack.

(Q) The processor finishes the execution of the current instruction.

(R) The processor executes the interrupt service routine.

(S) The processor pops the process status of L from the control stack.

(T) The processor loads the new PC value based on the interrupt.

Which one of the following is the correct order in which the events above occur? (2018)

(a) QPTRS

(b) PTRSQ

(c) TRPQS

(d) QTPRS

Ans: (a)

Sol:

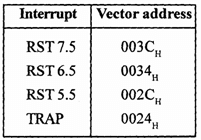

Q4: Which interrupt in 8085 Microprocessor is unmaskable? (2017)

(a) RST 5.5

(b) RST 7.5

(c) TRAP

(d) Both (A) and (B)

Ans: (c)

Sol: There are five interrupt input TRAP,RST 75,SRT 65,RST 55 and IWTR.

TRAP is a nonmaskable interrupt, that is, it cannot be disabled by an instruction

RST75,65,55 and INTR are maskable interrupt i.e. they can be enabled or disabled by software.

Q5: In 8085 microprocessor, the ISR for handling trap interrupt is at which location? (2013)

(a) 3CH

(b) 34H

(c) 74H

(d) 24H

Ans: (d)

Sol:

Q6: A computer handles several interrupt sources of which the following are relevant for this question.

Interrupt from CPU temperature sensor (raises interrupt if CPU temperature is too high)

Interrupt from Mouse (raises Interrupt if the mouse is moved or a button is pressed)

Interrupt from Keyboard (raises Interrupt if a key is pressed or released)

Interrupt from Hard Disk (raises Interrupt when a disk read is completed)

Which one of these will be handled at the HIGHEST priority? (2011)

(a) Interrupt from Hard Disk

(b) Interrupt from Mouse

(c) Interrupt from Keyboard

(d) Interrupt from CPU temp sensor

Ans: (d)

Sol: Higher priority interrupt levels are assigned to requests which, if delayed or interrupted,could have serious consequences. Devices with high speed transfer such as magnetic disks are given high priority, and slow devices such as keyboard receive low priority. We know that mouse pointer movements are more frequent than keyboard ticks. So its obvious that its data transfer rate is higher than keyboard. Delaying a CPU temperature sensor could have serious consequences, overheat can damage CPU circuitry. From the above information we can conclude that priorities are-

CPU temperature sensor > Hard Disk > Mouse > Keyboard

|

20 videos|113 docs|48 tests

|

|

20 videos|113 docs|48 tests

|

|

Explore Courses for Computer Science Engineering (CSE) exam

|

|