Computer Science Engineering (CSE) Exam > Computer Science Engineering (CSE) Tests > Test: Cache & Main Memory- 1 - Computer Science Engineering (CSE) MCQ

Test: Cache & Main Memory- 1 - Computer Science Engineering (CSE) MCQ

Test Description

10 Questions MCQ Test - Test: Cache & Main Memory- 1

Test: Cache & Main Memory- 1 for Computer Science Engineering (CSE) 2025 is part of Computer Science Engineering (CSE) preparation. The Test: Cache & Main Memory- 1 questions and answers have been prepared

according to the Computer Science Engineering (CSE) exam syllabus.The Test: Cache & Main Memory- 1 MCQs are made for Computer Science Engineering (CSE) 2025 Exam.

Find important definitions, questions, notes, meanings, examples, exercises, MCQs and online tests for Test: Cache & Main Memory- 1 below.

Solutions of Test: Cache & Main Memory- 1 questions in English are available as part of our course for Computer Science Engineering (CSE) & Test: Cache & Main Memory- 1 solutions in

Hindi for Computer Science Engineering (CSE) course.

Download more important topics, notes, lectures and mock test series for Computer Science Engineering (CSE) Exam by signing up for free. Attempt Test: Cache & Main Memory- 1 | 10 questions in 30 minutes | Mock test for Computer Science Engineering (CSE) preparation | Free important questions MCQ to study for Computer Science Engineering (CSE) Exam | Download free PDF with solutions

Test: Cache & Main Memory- 1 - Question 1

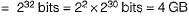

A 32-bit address bus allows access to a memory of capacity

Detailed Solution for Test: Cache & Main Memory- 1 - Question 1

Detailed Solution for Test: Cache & Main Memory- 1 - Question 2

Detailed Solution for Test: Cache & Main Memory- 1 - Question 3

Detailed Solution for Test: Cache & Main Memory- 1 - Question 4

Test: Cache & Main Memory- 1 - Question 5

Which of the following lists memory types from highest to lowest access speed?

Detailed Solution for Test: Cache & Main Memory- 1 - Question 5

Test: Cache & Main Memory- 1 - Question 6

According to temporal locality, processes are likely to reference pages that ____.

Detailed Solution for Test: Cache & Main Memory- 1 - Question 6

Test: Cache & Main Memory- 1 - Question 7

In caching system, the memory reference made in any short time interval tend to use only a small fraction of the total memory is called ______ .

Detailed Solution for Test: Cache & Main Memory- 1 - Question 7

Test: Cache & Main Memory- 1 - Question 8

Consider an (n + k) bit instruction with a k-bit opcode and single n-bit address. Then this instruction allow_______operations and_______ addressable memory cells.

Detailed Solution for Test: Cache & Main Memory- 1 - Question 8

Test: Cache & Main Memory- 1 - Question 9

Which of the following statements is false about dynamic RAM?

Detailed Solution for Test: Cache & Main Memory- 1 - Question 9

Test: Cache & Main Memory- 1 - Question 10

Which of the following statements is false with regard to fully associative and direct mapped cache organizations?

Detailed Solution for Test: Cache & Main Memory- 1 - Question 10

Information about Test: Cache & Main Memory- 1 Page

In this test you can find the Exam questions for Test: Cache & Main Memory- 1 solved & explained in the simplest way possible.

Besides giving Questions and answers for Test: Cache & Main Memory- 1, EduRev gives you an ample number of Online tests for practice

Download as PDF