Test: Sequential Logic Circuits- 1 - Electronics and Communication Engineering (ECE) MCQ

10 Questions MCQ Test - Test: Sequential Logic Circuits- 1

For which of the following flip-flops, the output is clearly defined for all combinations of two inputs?

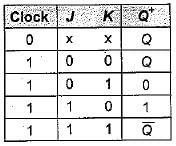

What J-K input condition will always set ‘Q+ upon the occurrence of the active clock transition ?

The output of S-R flip-flop when S = 1, R = 0 is

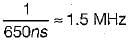

An eight stage ripple counter uses a flip-flop with propagation delay of 75 nano-seconds. The pulse width of the strobe is 50 nano-seconds. The frequency of the input signal which can be used for proper operation of the counter is approximately equal to

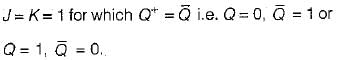

The output of a J-K flip-flop with asynchronous preset and clear inputs if ‘1 ’. The output can be changed to ‘0’ with which one of the following conditions?

A J-K flip-flop can be implemented using D flip- flop connected such that

Assertion (A): In general, asynchronous circuits are considerably faster than synchronous circuits.

Reason (R): In an asynchronous circuit, events can occur after one event is completed and there is no need to wait for a clock pulse.

Consider the following statements:

1. Sequential circuits are always faster than combination circuits.

2. In an asynchronous circuit there is no problem of stability.

3. The logic circuits whose outputs at any instant of time depend only on the input signals present at that time are known as combinational circuits.

4. In a combinational circuit, for a change in the input, the output appears immediately.

5. In a sequential circuits, the output signals are fed back to the input side.

Which of the statement given above are correct?

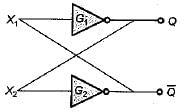

Assertion (A): A latch is a memory device with the capability of storing one binary digit of information.

Reason (R): A basic latch is made up of cross coupled inverters.