Combinational Logic Circuits - Free MCQ Practice Test with solutions, GATE

MCQ Practice Test & Solutions: Test: Combinational Logic Circuits (10 Questions)

You can prepare effectively for Electrical Engineering (EE) Analog and Digital Electronics with this dedicated MCQ Practice Test (available with solutions) on the important topic of "Test: Combinational Logic Circuits". These 10 questions have been designed by the experts with the latest curriculum of Electrical Engineering (EE) 2026, to help you master the concept.

Test Highlights:

- - Format: Multiple Choice Questions (MCQ)

- - Duration: 30 minutes

- - Number of Questions: 10

Sign up on EduRev for free to attempt this test and track your preparation progress.

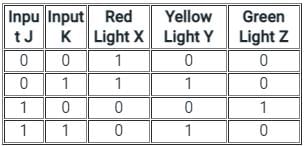

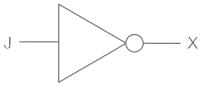

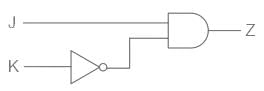

A combinational logic circuit for traffic control is designed. ___________ GATE can only be used to implement the designed control circuit without any additional GATES.

Detailed Solution: Question 1

In the figure shown, D0 and D1 are digital inputs, S is a control input and Y is the output. When S = 0, then Y = D0. When S = 1, then Y = D1. The given combinational circuit is

Detailed Solution: Question 2

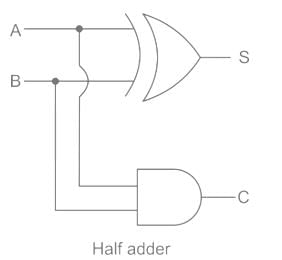

_______ are an example of a combinational circuit.

Detailed Solution: Question 3

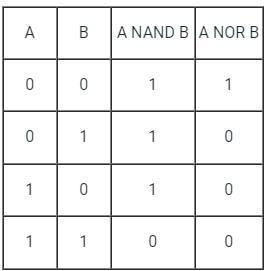

Any combinational circuit can be designed using only

Detailed Solution: Question 4

Detailed Solution: Question 5

Number of 2 × 1 Multiplexers are required to implement 64 × 1 Multiplexers

Detailed Solution: Question 6

Detailed Solution: Question 7

In a 1 to 4 De-multiplexer, how many select input lines are required?

Detailed Solution: Question 8

Detailed Solution: Question 9

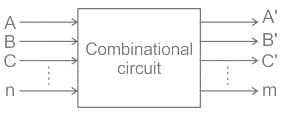

What determines the output from the combinational logic circuit in Digital Electronics?

Detailed Solution: Question 10

135 videos|183 docs|71 tests |