Electrical Engineering (EE) Exam > Electrical Engineering (EE) Tests > Test: Flip Flops - Electrical Engineering (EE) MCQ

Test: Flip Flops - Electrical Engineering (EE) MCQ

Test Description

15 Questions MCQ Test - Test: Flip Flops

Test: Flip Flops for Electrical Engineering (EE) 2025 is part of Electrical Engineering (EE) preparation. The Test: Flip Flops questions and answers have been prepared

according to the Electrical Engineering (EE) exam syllabus.The Test: Flip Flops MCQs are made for Electrical Engineering (EE) 2025 Exam.

Find important definitions, questions, notes, meanings, examples, exercises, MCQs and online tests for Test: Flip Flops below.

Solutions of Test: Flip Flops questions in English are available as part of our course for Electrical Engineering (EE) & Test: Flip Flops solutions in

Hindi for Electrical Engineering (EE) course.

Download more important topics, notes, lectures and mock test series for Electrical Engineering (EE) Exam by signing up for free. Attempt Test: Flip Flops | 15 questions in 30 minutes | Mock test for Electrical Engineering (EE) preparation | Free important questions MCQ to study for Electrical Engineering (EE) Exam | Download free PDF with solutions

Test: Flip Flops - Question 1

Latches constructed with NOR and NAND gates tend to remain in the latched condition due to which configuration feature?

Detailed Solution for Test: Flip Flops - Question 1

Detailed Solution for Test: Flip Flops - Question 2

Test: Flip Flops - Question 3

The logic circuits whose outputs at any instant of time depends only on the present input but also on the past outputs are called ________________

Detailed Solution for Test: Flip Flops - Question 3

Detailed Solution for Test: Flip Flops - Question 4

Detailed Solution for Test: Flip Flops - Question 5

Test: Flip Flops - Question 6

The output of latches will remain in set/reset untill ___________

Detailed Solution for Test: Flip Flops - Question 6

Test: Flip Flops - Question 7

The circuits of NOR based S-R latch classified as asynchronous sequential circuits, why?

Detailed Solution for Test: Flip Flops - Question 7

Detailed Solution for Test: Flip Flops - Question 8

Test: Flip Flops - Question 9

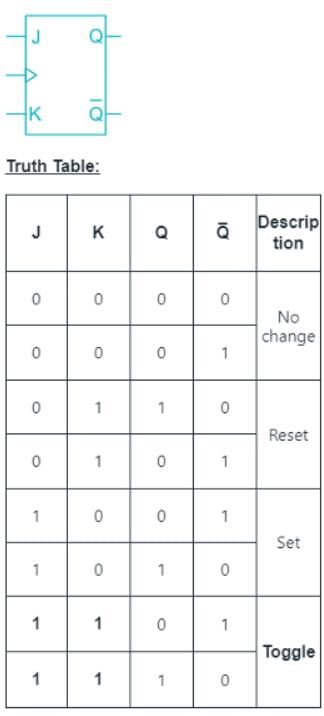

When both inputs of a J-K flip-flop cycle are high, the output will ___________

Detailed Solution for Test: Flip Flops - Question 9

Test: Flip Flops - Question 10

A basic S-R flip-flop can be constructed by cross-coupling of which basic logic gates?

Detailed Solution for Test: Flip Flops - Question 10

Detailed Solution for Test: Flip Flops - Question 11

Detailed Solution for Test: Flip Flops - Question 12

Detailed Solution for Test: Flip Flops - Question 13

Detailed Solution for Test: Flip Flops - Question 14

Test: Flip Flops - Question 15

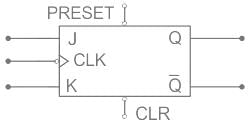

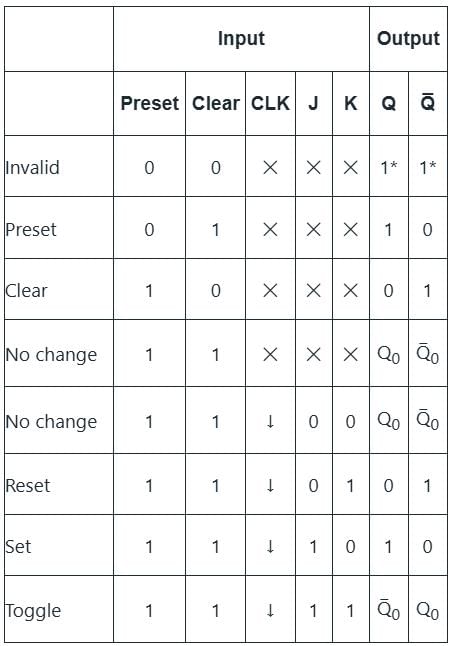

When two asynchronous active low inputs PRESET and CLEAR are applied to a J-K flip flop the output will be

Detailed Solution for Test: Flip Flops - Question 15

Information about Test: Flip Flops Page

In this test you can find the Exam questions for Test: Flip Flops solved & explained in the simplest way possible.

Besides giving Questions and answers for Test: Flip Flops, EduRev gives you an ample number of Online tests for practice

Download as PDF