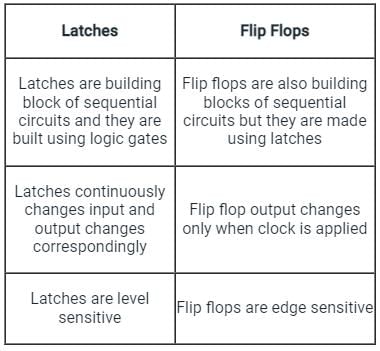

Test: S-R Latch - Electrical Engineering (EE) MCQ

15 Questions MCQ Test - Test: S-R Latch

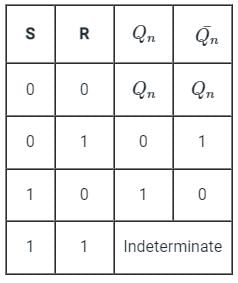

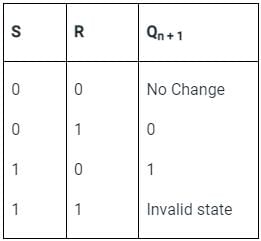

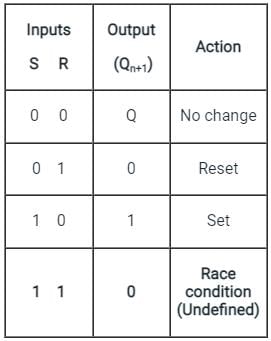

When both the inputs of a latch are high, the output is unpredictable. What is this condition called?

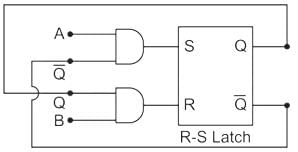

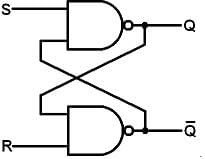

The two inputs A and B are connected to a NOR based R-S latch, via two AND gates as shown in the figure. If A = 1 and B = 0, the output QQ̅ is

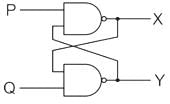

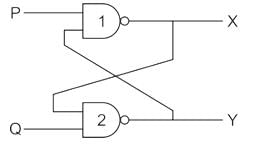

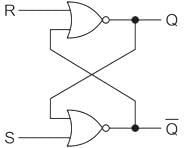

In the latch circuit shown, the NAND gates have non-zero, but unequal propagation delays. The present input conditions is: P = Q = ‘0’. If the input conditions is changed simultaneously to P = Q = ‘1’, the outputs X and Y are

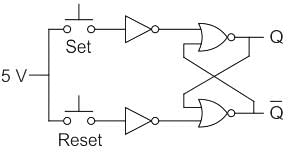

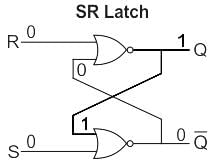

An SR latch is implemented using TTL gates as shown in the figure. The set and reset pulse inputs are provided using the push-button switches. It is observed that the circuit fails to work as desired. The SR latch can be made functional by changing

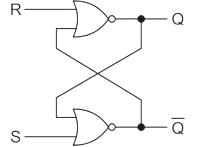

The first step of the analysis procedure of SR latch is to ___________

When both inputs of SR latches are high, the latch goes ___________

When a high is applied to the Set line of an SR latch, then ___________

.

.