Electrical Engineering (EE) Exam > Electrical Engineering (EE) Tests > Test: Half Adder - Electrical Engineering (EE) MCQ

Test: Half Adder - Electrical Engineering (EE) MCQ

Test Description

10 Questions MCQ Test - Test: Half Adder

Test: Half Adder for Electrical Engineering (EE) 2025 is part of Electrical Engineering (EE) preparation. The Test: Half Adder questions and answers have been prepared

according to the Electrical Engineering (EE) exam syllabus.The Test: Half Adder MCQs are made for Electrical Engineering (EE) 2025 Exam.

Find important definitions, questions, notes, meanings, examples, exercises, MCQs and online tests for Test: Half Adder below.

Solutions of Test: Half Adder questions in English are available as part of our course for Electrical Engineering (EE) & Test: Half Adder solutions in

Hindi for Electrical Engineering (EE) course.

Download more important topics, notes, lectures and mock test series for Electrical Engineering (EE) Exam by signing up for free. Attempt Test: Half Adder | 10 questions in 30 minutes | Mock test for Electrical Engineering (EE) preparation | Free important questions MCQ to study for Electrical Engineering (EE) Exam | Download free PDF with solutions

Test: Half Adder - Question 1

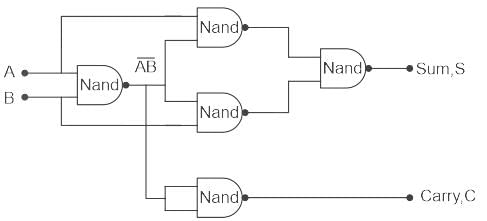

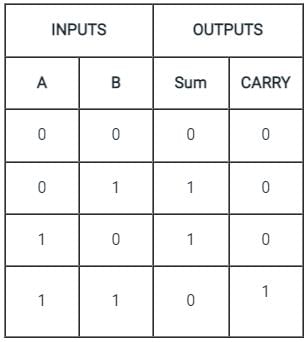

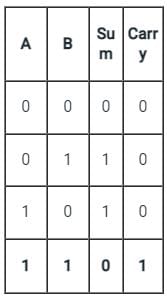

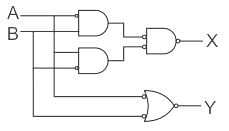

How many number of 2-input NAND gates are required to realise a half adder circuit?

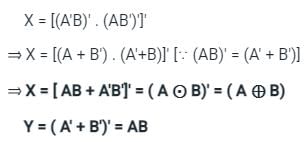

Detailed Solution for Test: Half Adder - Question 1

Test: Half Adder - Question 2

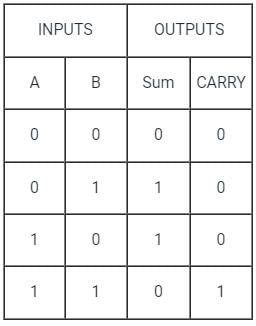

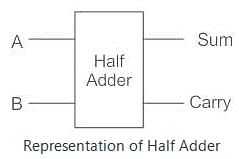

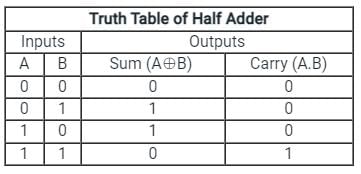

Half adder is a logic circuit that accepts ________ single bit inputs.

Detailed Solution for Test: Half Adder - Question 2

Detailed Solution for Test: Half Adder - Question 3

Test: Half Adder - Question 4

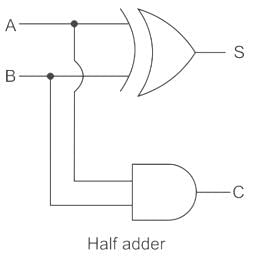

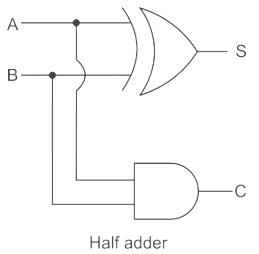

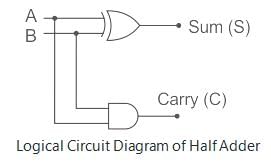

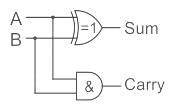

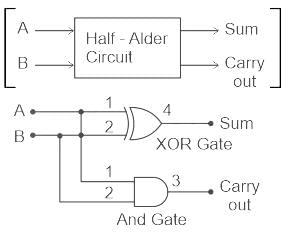

Half adder circuit can be produced using a two-input ______ gate and a two-input ______ gate.

Detailed Solution for Test: Half Adder - Question 4

Detailed Solution for Test: Half Adder - Question 5

Test: Half Adder - Question 6

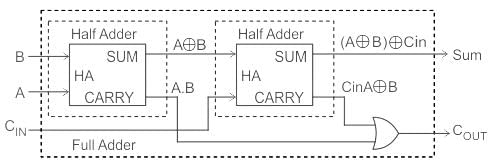

The logic circuit of binary adder which is used to add 4-bits binary numbers, requires _________ half adder (s) and ________ full adder(s).

Detailed Solution for Test: Half Adder - Question 6

Detailed Solution for Test: Half Adder - Question 7

Detailed Solution for Test: Half Adder - Question 8

Test: Half Adder - Question 9

A ________ arithmetic circuit adds two binary digits, giving a sum bit and a carry bit.

Detailed Solution for Test: Half Adder - Question 9

Detailed Solution for Test: Half Adder - Question 10

Information about Test: Half Adder Page

In this test you can find the Exam questions for Test: Half Adder solved & explained in the simplest way possible.

Besides giving Questions and answers for Test: Half Adder, EduRev gives you an ample number of Online tests for practice

Download as PDF