Test: Sample & Hold Circuits - Electronics and Communication Engineering (ECE) MCQ

10 Questions MCQ Test - Test: Sample & Hold Circuits

A good Sample and Hold circuit should have

1. High input impedance

2. High output impedance

3. Low input impedance

4. Low output impedance

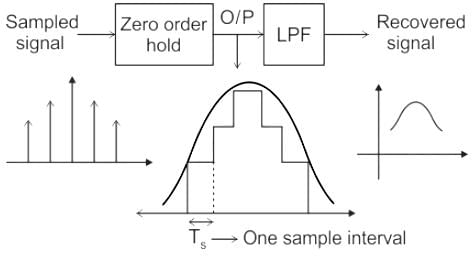

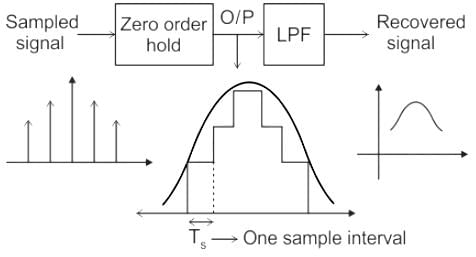

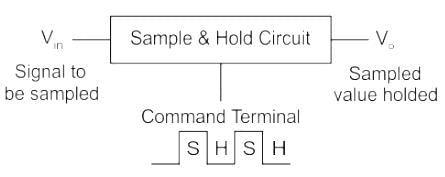

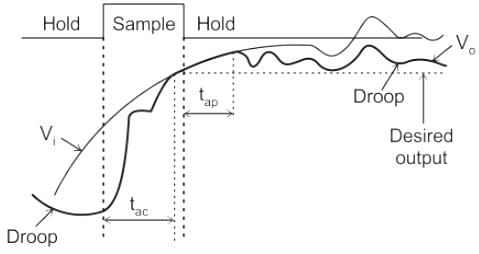

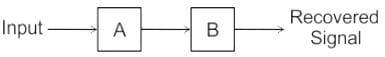

Figure shows 4 block diagram of a system to recover a sampled signal shown as input.

Blocks A and B can be respectively :

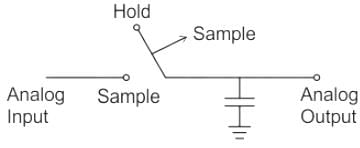

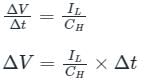

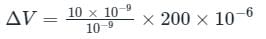

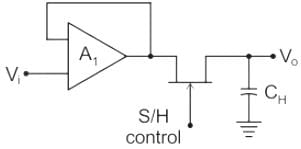

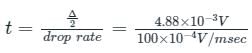

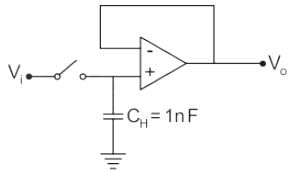

The figure shown below is a sample and hold circuit used at a sampling rate of 1 kHz with an A / D converter having conversion time of 200 μ sec. The op-amp has an input bias current of 10 nA. The maximum hold error (in mV) is ________.

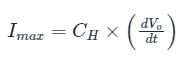

For a given sample-and-hold circuit, if the value of the hold capacitor is increased, then

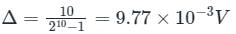

A signal channel signal acquisition system with 0-10 V range consist of a sample and hold circuit with worst case drop rate of 100 μV/ms and 10 bit ADC. The maximum conversion time for the ADC is

When a time-varying signal has to be digitized using an ADC, which of the following is necessary to use before digitization?

In A/D converter, what is the time relation between sampling period T and the duration of the sample mode and the hold mode?