Test: Machine Instructions & Addressing Modes - Electronics and Communication Engineering (ECE) MCQ

10 Questions MCQ Test - Test: Machine Instructions & Addressing Modes

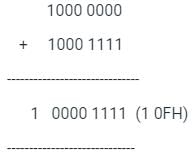

In 8051, the accumulator register contains 80H and B register contains 8FH. The content of the accumulator and status of the carry flag after the addition operation are respectively

Which of the following statements is/are true?

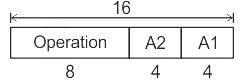

Only instructions with zero, one, and two addresses are supported by some CPUs. The size of an op-code is 16 bits, whereas the size of an address is 4 bits.

What is the Maximum number of two address instructions?

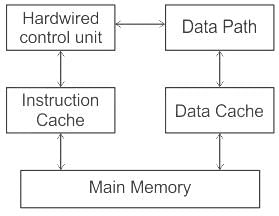

Which one of the following is a special characteristic of RISC processor?

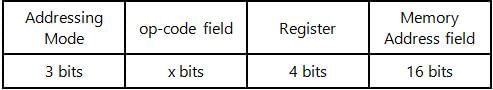

A CPU has 12 registers and uses 6 addressing modes. RAM is 64K × 32. What is the maximum size of the op-code field if the instruction has a register operand and a memory address operand?

The following language uses mnemonic OP codes

A processor has 300 distinct instructions and 70 general-purpose registers. A 32-bit instruction word has an opcode, two register operands, and an immediate operand. The number of bits available for the immediate operand field is_____

Which of the following statements is/are true?

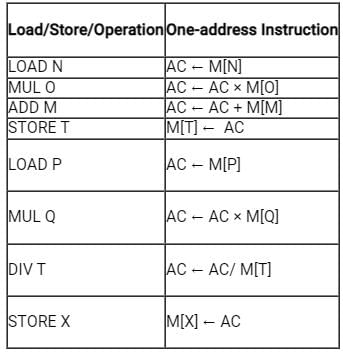

In X = (M + N × O) / (P × Q), how many one-address instructions are required to evaluate it?