Electronics and Communication Engineering (ECE) Exam > Electronics and Communication Engineering (ECE) Tests > Test: D Flip Flop - Electronics and Communication Engineering (ECE) MCQ

Test: D Flip Flop - Electronics and Communication Engineering (ECE) MCQ

Test Description

15 Questions MCQ Test - Test: D Flip Flop

Test: D Flip Flop for Electronics and Communication Engineering (ECE) 2025 is part of Electronics and Communication Engineering (ECE) preparation. The Test: D Flip Flop questions and answers have been prepared

according to the Electronics and Communication Engineering (ECE) exam syllabus.The Test: D Flip Flop MCQs are made for Electronics and Communication Engineering (ECE) 2025 Exam.

Find important definitions, questions, notes, meanings, examples, exercises, MCQs and online tests for Test: D Flip Flop below.

Solutions of Test: D Flip Flop questions in English are available as part of our course for Electronics and Communication Engineering (ECE) & Test: D Flip Flop solutions in

Hindi for Electronics and Communication Engineering (ECE) course.

Download more important topics, notes, lectures and mock test series for Electronics and Communication Engineering (ECE) Exam by signing up for free. Attempt Test: D Flip Flop | 15 questions in 45 minutes | Mock test for Electronics and Communication Engineering (ECE) preparation | Free important questions MCQ to study for Electronics and Communication Engineering (ECE) Exam | Download free PDF with solutions

Test: D Flip Flop - Question 1

Why do the D flip-flops receive its designation or nomenclature as ‘Data Flip-flops’?

Detailed Solution for Test: D Flip Flop - Question 1

Test: D Flip Flop - Question 2

A D flip-flop utilizing a PGT clock is in the CLEAR state. Which of the following input actions will cause it to change states?

Detailed Solution for Test: D Flip Flop - Question 2

Detailed Solution for Test: D Flip Flop - Question 3

Detailed Solution for Test: D Flip Flop - Question 4

Test: D Flip Flop - Question 5

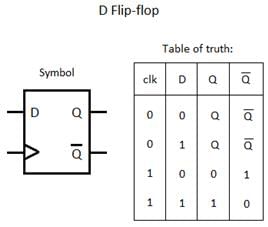

In D flip-flop, if clock input is HIGH & D=1, then output is ___________

Detailed Solution for Test: D Flip Flop - Question 5

Detailed Solution for Test: D Flip Flop - Question 6

Detailed Solution for Test: D Flip Flop - Question 7

Test: D Flip Flop - Question 8

The characteristic equation of D-flip-flop implies that ___________

Detailed Solution for Test: D Flip Flop - Question 8

Test: D Flip Flop - Question 9

A positive edge-triggered D flip-flop will store a 1 when ________

Detailed Solution for Test: D Flip Flop - Question 9

Test: D Flip Flop - Question 10

Which of the following describes the operation of a positive edge-triggered D flip-flop?

Detailed Solution for Test: D Flip Flop - Question 10

Detailed Solution for Test: D Flip Flop - Question 11

Test: D Flip Flop - Question 12

Which statement describes the BEST operation of a negative-edge-triggered D flip-flop?

Detailed Solution for Test: D Flip Flop - Question 12

Detailed Solution for Test: D Flip Flop - Question 13

Detailed Solution for Test: D Flip Flop - Question 14

Detailed Solution for Test: D Flip Flop - Question 15

Information about Test: D Flip Flop Page

In this test you can find the Exam questions for Test: D Flip Flop solved & explained in the simplest way possible.

Besides giving Questions and answers for Test: D Flip Flop, EduRev gives you an ample number of Online tests for practice

Download as PDF